- 您现在的位置:买卖IC网 > PDF目录10760 > MAX5556GSA+ (Maxim Integrated Products)IC DAC STEREO AUDIO 8-SOIC PDF资料下载

参数资料

| 型号: | MAX5556GSA+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 3/17页 |

| 文件大小: | 0K |

| 描述: | IC DAC STEREO AUDIO 8-SOIC |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 100 |

| 位数: | 16 |

| 数据接口: | I²S,串行 |

| 转换器数目: | 2 |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOIC |

| 包装: | 管件 |

| 输出数目和类型: | 2 电压,单极 |

| 采样率(每秒): | * |

MAX5556

Low-Cost Stereo Audio DAC

11

Maxim Integrated

Left/Right Clock Input (LRCLK)

LRCLK is the left/right clock input signal for the 3-wire

interface and sets the sample frequency (fS). On the

MAX5556, drive LRCLK low to direct data to OUTL or

LRCLK high to direct data to OUTR (Figure 4). The

MAX5556 accepts data at LRCLK audio sample rates

from 2kHz to 50kHz.

Master Clock (MCLK)

MCLK accepts the master clock signal from an external

clocking device and is used to derive internal clock fre-

quencies. Set the MCLK/LRCLK ratio to 256, 384, or

512 to achieve the internal serial clock frequencies list-

ed in Table 1. Table 2 details the MCLK/LRCLK ratios

for three sample audio rates.

The MAX5556 detects the MCLK/LRCLK ratio during

the initialization sequence by counting the number of

MCLK transitions during a single LRCLK period. MCLK,

SCLK, and LRCLK must be synchronous signals.

Data Formats

MAX5556 I2S Left-Justified Data Format

The MAX5556 accepts data with an I2S left-justified

data format, accepting 16 or 24 bits of data. SDATA

accepts data in two’s complement format with the MSB

first. The MSB is valid on the second SCLK rising edge

after LRCLK transitions low to high or high to low

(Figure 4). Drive LRCLK low to direct data to OUTL.

Drive LRCLK high to direct data to OUTR. The number

of SCLK pulses with LRCLK high or low determines the

number of bits transferred per sample. If fewer than 24

bits of data are written, the remaining LSBs are set to 0.

If more than 24 bits are written, any bits after the LSB

are ignored.

The MAX5556 accepts up to 24 bits of data in external

serial clock mode or when the MCLK/LRCLK ratio is

384 (internal serial clock = 48 x fS) in internal serial

clock mode. The DAC also accepts 16 bits of data in

internal serial clock mode when the MCLK/LRCLK ratio

is 256 or 512 (internal serial clock = 32 x fS).

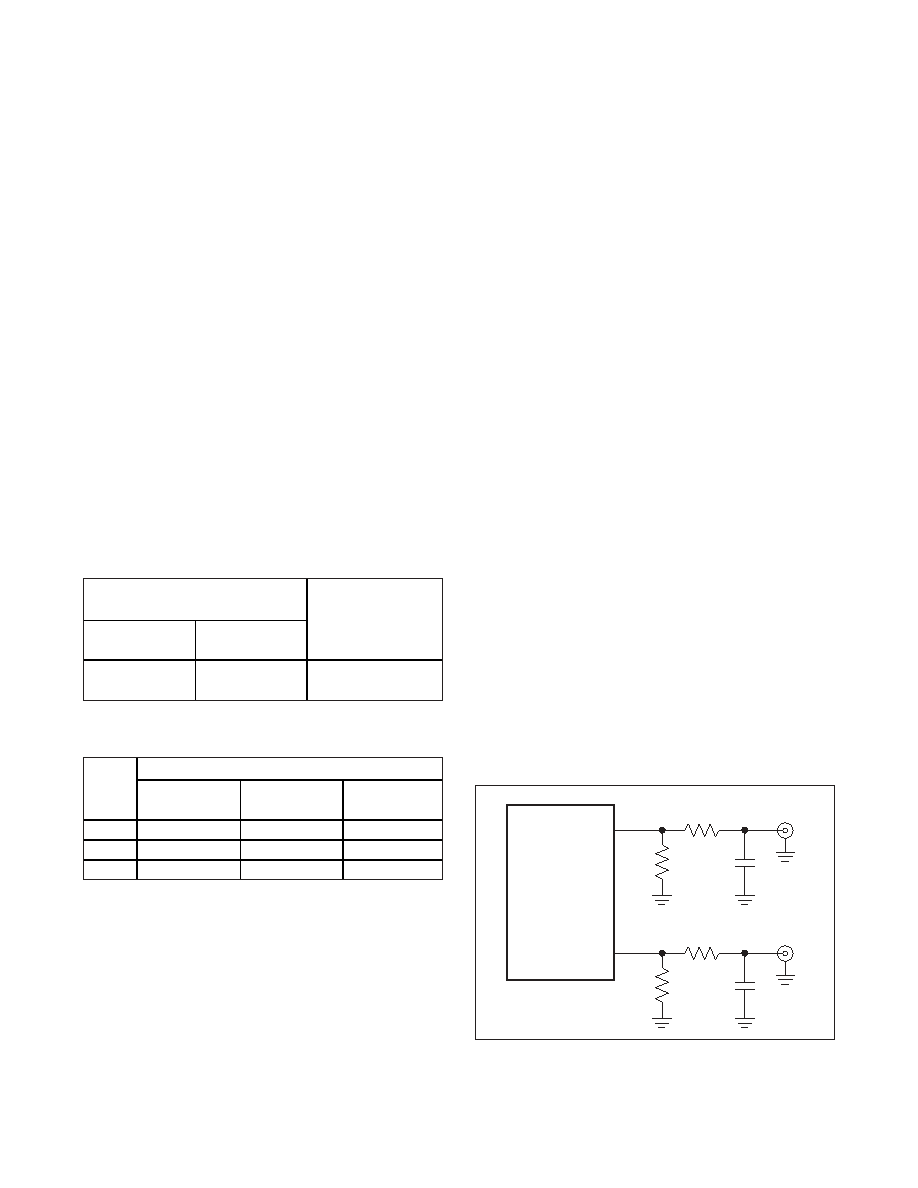

External Analog Filter

Use an external lowpass analog filter to further reduce

harmonic images, noise, and spurs. The external analog

filter can be either active or passive depending upon

performance and design requirements. For example fil-

ters, see Figures 8 and 9 and the

Applications

Information section. Careful attention should be paid

when selecting capacitors for audio signal path applica-

tions. NPO and C0G types are recommended as are alu-

minum electrolytics and low-ESR tantalum varieties. Use

of generic ceramic types is not recommended and may

result in degraded THD performance. Always consult

manufacturers’ data sheets and applications information.

Table 1. Internal and External Clock

Frequencies

INTERNAL SERIAL

CLOCK FREQUENCY

MCLK/LRCLK

= 256 OR 512

MCLK/LRCLK

= 384

EXTERNAL SERIAL

CLOCK FREQUENCY

32 x fS

48 x fS

User defined

(Figure 4)

Table 2. MCLK/LRCLK Ratios

MCLK (MHz)

LRCLK

(kHz)

MCLK/LRCLK

= 256

MCLK/LRCLK

= 384

MCLK/LRCLK

= 512

32

8.1920

12.2880

16.3840

44.1

11.2896

16.9344

22.5792

48

12.2880

18.4320

24.5760

MAX5556

OUTR

OUTL

100k

Ω

100k

Ω

R = 560

Ω

R = 560

Ω

C = 1.5nF

Figure 8. Passive Component Analog Output Filter

相关PDF资料 |

PDF描述 |

|---|---|

| VI-2NM-CU-F1 | CONVERTER MOD DC/DC 10V 200W |

| VI-2NK-CU-F2 | CONVERTER MOD DC/DC 40V 200W |

| VI-2NJ-IW-S | CONVERTER MOD DC/DC 36V 100W |

| MX7248JP+ | IC DAC 12BIT MULT 20-PLCC |

| VE-B6D-MX-F3 | CONVERTER MOD DC/DC 85V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX5556GSA+ | 功能描述:IC DAC STEREO AUDIO 8-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:3,000 系列:nanoDAC™ 设置时间:80µs 位数:18 数据接口:DSP,MICROWIRE?,QSPI?,串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:SOT-23-8 供应商设备封装:SOT-23-8 包装:带卷 (TR) 输出数目和类型:1 电压,单极 采样率(每秒):- 产品目录页面:784 (CN2011-ZH PDF) 配用:EVAL-AD5680EBZ-ND - BOARD EVAL FOR AD5680 其它名称:AD5680BRJZ-2REEL7TR |

| MAX555CCB+D | 功能描述:数模转换器- DAC 300Msps 12-Bit DAC with Complementary Voltage Outputs RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| MAX555CCB+TD | 功能描述:数模转换器- DAC 300Msps 12-Bit DAC with Complementary Voltage Outputs RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| MAX555CCB-D | 功能描述:数模转换器- DAC 300Msps 12-Bit DAC with Complementary Voltage Outputs RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| MAX555CCB-TD | 功能描述:数模转换器- DAC NULL RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。