- 您现在的位置:买卖IC网 > PDF目录11685 > MAX9220EUM+D (Maxim Integrated Products)IC DESERIALIZER PROG 48TSSOP PDF资料下载

参数资料

| 型号: | MAX9220EUM+D |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 4/17页 |

| 文件大小: | 0K |

| 描述: | IC DESERIALIZER PROG 48TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 39 |

| 功能: | 解串器 |

| 数据速率: | 1.785Gbps |

| 输入类型: | LVDS |

| 输出类型: | LVTTL,LVCMOS |

| 输入数: | 3 |

| 输出数: | 21 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TFSOP(0.240",6.10mm 宽) |

| 供应商设备封装: | 48-TSSOP |

| 包装: | 管件 |

MAX9210/MAX9214/MAX9220/MAX9222

Programmable DC-Balance

21-Bit Deserializers

12

______________________________________________________________________________________

The transition time in a real system depends on the fre-

quency response of the cable driven by the serializer.

The capacitor value decreases for a higher frequency

parallel clock and for higher levels of droop and jitter.

Use high-frequency, surface-mount ceramic capacitors.

Equation 1 altered for four series capacitors (Figure 13) is:

C = - (4 x tB x DSV)/(ln (1 - D) x (RT + RO)) (Eq 3)

Fail-Safe

The MAX9210/MAX9214/MAX9220/MAX9222 have fail-

safe LVDS inputs in non-DC-balanced mode (Figure 1).

Fail-safe drives the outputs low when the correspond-

ing LVDS input is open, undriven and shorted, or

undriven and parallel terminated. The fail-safe on the

LVDS clock input drives all outputs low. Fail-safe does

not operate in DC-balanced mode.

Input Bias and Frequency Detection

In DC-balanced mode, the inverting and noninverting

LVDS inputs are internally connected to +1.2V through

42k

Ω (min) to provide biasing for AC-coupling (Figure 1).

A frequency-detection circuit on the clock input detects

when the input is not switching, or is switching at low

frequency. In this case, all outputs are driven low. To

prevent switching due to noise when the clock input is

not driven, bias the clock input to differential +15mV by

connecting a 10k

Ω ±1% pullup resistor between the

noninverting input and VCC, and a 10k

Ω ±1% pulldown

resistor between the inverting input and ground. These

bias resistors, along with the 100

Ω ±1% tolerance ter-

mination resistor, provide +15mV of differential input.

However, the +15mV bias causes degradation of

RSKM proportional to the slew rate of the clock input.

For example, if the clock transitions 250mV in 500ps,

the slew rate of 0.5mV/ps reduces RSKM by 30ps.

Unused LVDS Data Inputs

In non-DC-balanced mode, leave unused LVDS data

inputs open. In non-DC balanced mode, the input fail-

safe circuit drives the corresponding outputs low and no

pullup or pulldown resistors are needed. In DC-balanced

mode, at each unused LVDS data input, pull the inverting

input up to VCC using a 10k

Ω resistor, and pull the nonin-

verting input down to ground using a 10k

Ω resistor. Do

not connect a termination resistor. The pullup and pull-

down resistors drive the corresponding outputs low and

prevent switching due to noise.

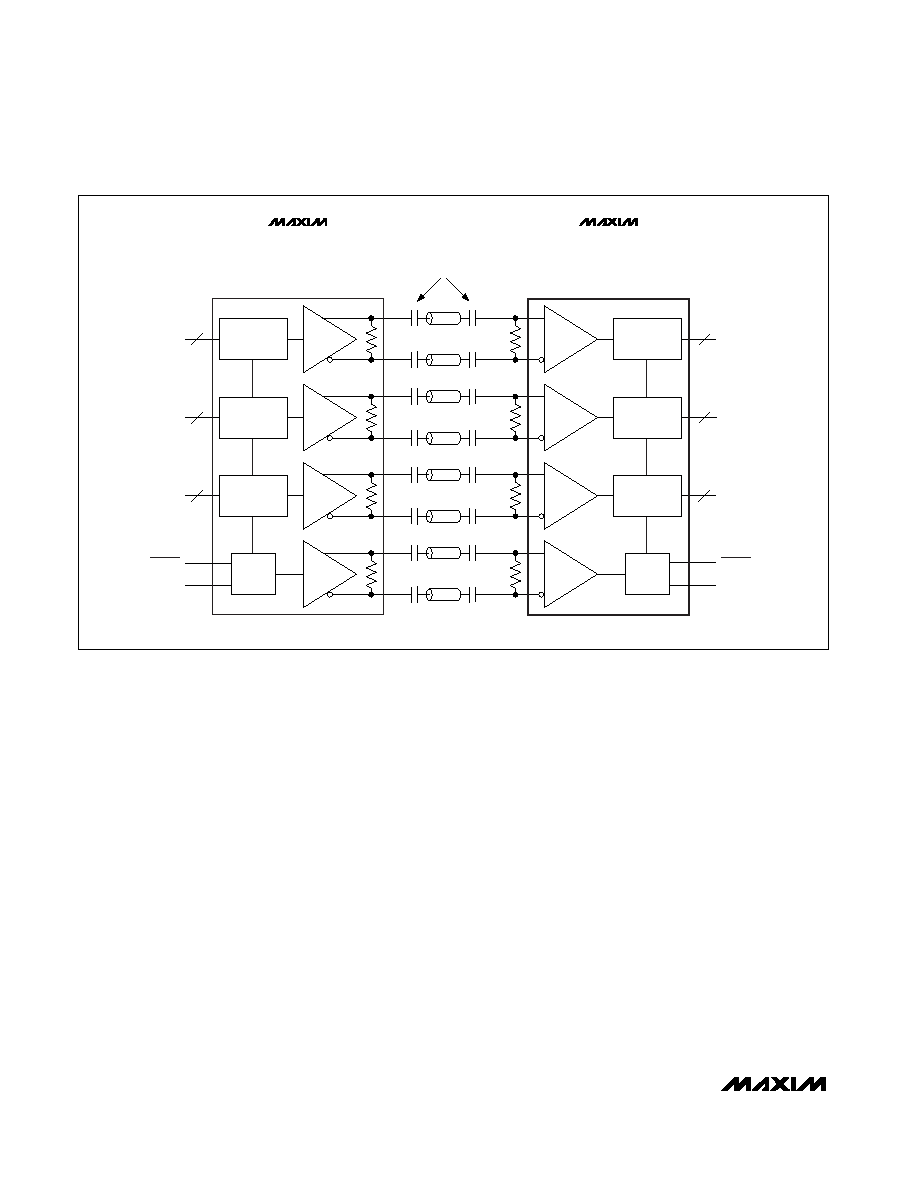

(7 + 2):1

1:(9 - 2)

7

100

Ω

(7 + 2):1

1:(9 - 2)

7

100

Ω

(7 + 2):1

1:(9 - 2)

7

100

Ω

PLL

100

Ω

MAX9209

MAX9213

MAX9210

MAX9214

MAX9220

MAX9222

TxOUT

TxCLK OUT

RxIN

RxCLK IN

21:3 SERIALIZER

3:21 DESERIALIZER

PWRDWN

RxCLK OUT

RxOUT

PWRDWN

TxCLK IN

TxIN

HIGH-FREQUENCY CERAMIC

SURFACE-MOUNT CAPACITORS

Figure 13. Four Capacitors per Link, AC-Coupled, DC-Balanced Mode

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9220EUM+ | IC DESERIALIZER PROG 48TSSOP |

| MAX9210EUM+D | IC DESERIALIZER PROG 48TSSOP |

| 031-5999-RFX | CONN PLUG BNC CRIMP LMR240 |

| MAX9248GCM/V+T | IC DESERIALIZR LVDS 27BIT 48TQFP |

| MAX9248GCM+T | IC DESERIALIZER LVDS 48-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9220EUM-T | 功能描述:串行器/解串器 - Serdes DC-Balanced Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9220EUM-TD | 功能描述:串行器/解串器 - Serdes DC-Balanced Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9222 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Programmable DC-Balance 21-Bit Deserializers |

| MAX9222ETM | 制造商:Maxim Integrated Products 功能描述:- Rail/Tube |

| MAX9222EUM | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Programmable DC-Balance 21-Bit Deserializers |

发布紧急采购,3分钟左右您将得到回复。