- 您现在的位置:买卖IC网 > PDF目录11684 > MAX9247GCM/V+T (Maxim Integrated Products)IC SERIALIZER LVDS 27BIT 48LQFP PDF资料下载

参数资料

| 型号: | MAX9247GCM/V+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 14/17页 |

| 文件大小: | 0K |

| 描述: | IC SERIALIZER LVDS 27BIT 48LQFP |

| 标准包装: | 2,000 |

| 系列: | * |

MAX9247

27-Bit, 2.5MHz-to-42MHz

DC-Balanced LVDS Serializer

6

_______________________________________________________________________________________

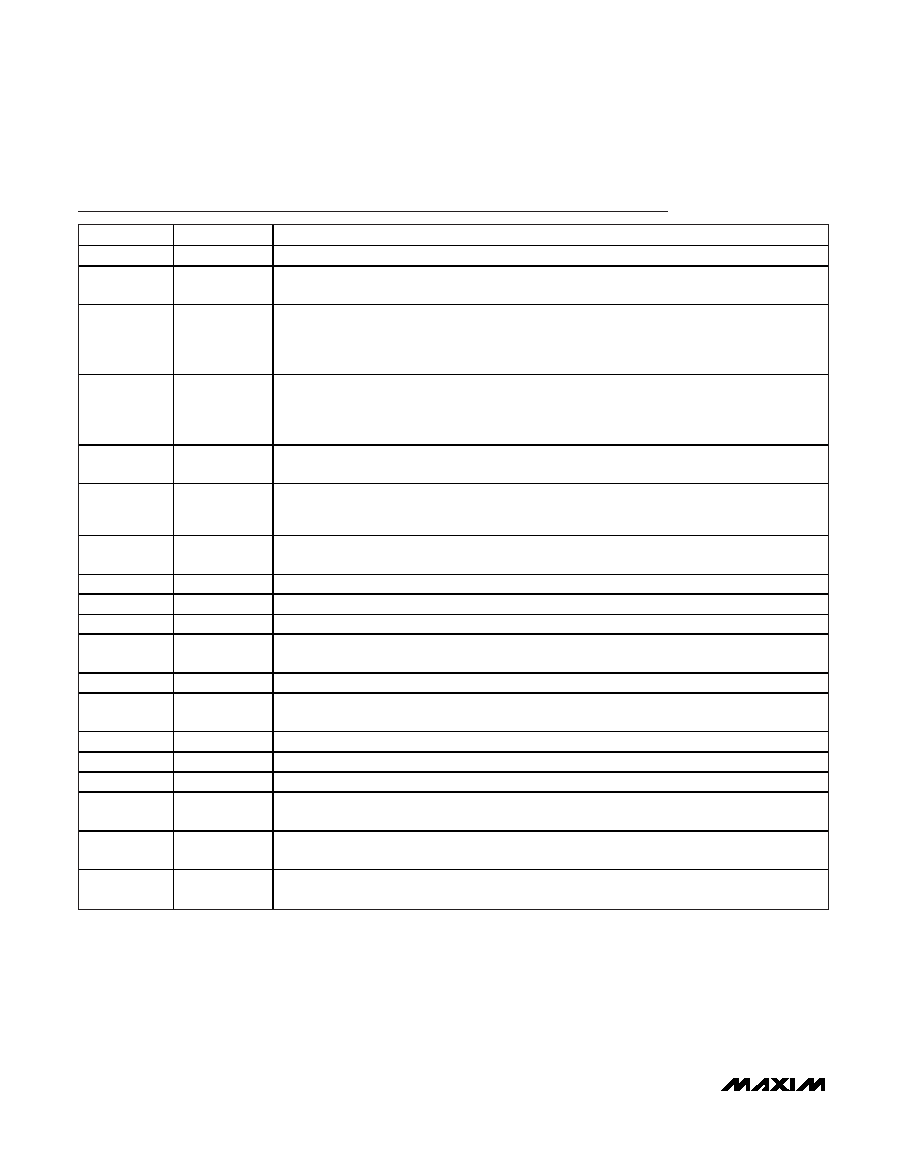

Pin Description

PIN

NAME

FUNCTION

1, 13, 37

GND

Input Buffer Supply and Digital Supply Ground

2VCCIN

Input Buffer Supply Voltage. Bypass to GND with 0.1F and 0.001F capacitors in parallel as

close to the device as possible, with the smallest value capacitor closest to the supply pin.

3–10,

39–48

RGB_IN10–

RGB_IN17,

RGB_IN0–

RGB_IN9

LVTTL/LVCMOS Red, Green, and Blue Digital Video Data Inputs. Eighteen data bits are loaded

into the input latch on the rising edge of PCLK_IN when DE_IN is high. Internally pulled down to

GND.

11, 12, 15–21

CNTL_IN0,

CNTL_IN1,

CNTL_IN2–

CNTL_IN8

LVTTL/LVCMOS Control Data Inputs. Control data are latched on the rising edge of PCLK_IN

when DE_IN is low. Internally pulled down to GND.

14, 38

VCC

Digital Supply Voltage. Bypass to GND with 0.1F and 0.001F capacitors in parallel as close to

the device as possible, with the smallest value capacitor closest to the supply pin.

22

DE_IN

LVTTL/LVCMOS Data-Enable Input. Logic-high selects RGB_IN[17:0] to be latched. Logic-low

selects CNTL_IN[8:0] to be latched. DE_IN must be switching for proper operation. Internally

pulled down to GND.

23

PCLK_IN

LVTTL/LVCMOS Parallel Clock Input. Latches data and control inputs and provides the PLL

reference clock. Internally pulled down to GND.

24

I.C.

Internally Connected. Leave unconnected for normal operation.

25

PRE

Preemphasis Enable Input. Drive PRE high to enable preemphasis.

26

PLLGND

PLL Supply Ground

27

VCCPLL

PLL Supply Voltage. Bypass to PLLGND with 0.1F and 0.001F capacitors in parallel as close to

the device as possible, with the smallest value capacitor closest to the supply pin.

28

PWRDWN

LVTTL/LVCMOS Power-Down Input. Internally pulled down to GND.

29

CMF

Common-Mode Filter. Optionally connect a capacitor between CMF and LVDSGND to filter

common-mode switching noise.

30, 31

LVDSGND

LVDS Supply Ground

32

OUT-

Inverting LVDS Serial-Data Output

33

OUT+

Noninverting LVDS Serial-Data Output

34

VCCLVDS

LVDS Supply Voltage. Bypass to LVDSGND with 0.1F and 0.001F capacitors in parallel as

close to the device as possible, with the smallest value capacitor closest to the supply pin.

35

RNG1

LVTTL/LVCMOS Frequency Range Select Input. Set to the frequency range that includes the

PCLK_IN frequency as shown in Table 3. Internally pulled down to GND.

36

RNG0

LVTTL/LVCMOS Frequency Range Select Input. Set to the frequency range that includes the

PCLK_IN frequency as shown in Table 3. Internally pulled down to GND.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9250GCM/V+T | IC DESERIALIZER LVDS 48LQFP |

| MAX9250GCM+T | IC DESERIALIZER LVDS 48-LQFP |

| MAX9247GCM+T | IC SERIALIZER LVDS 48-LQFP |

| D38999/24FG41SB | CONN RCPT 41POS JAM NUT W/SCKT |

| D38999/26FE99SA | CONN PLUG 23POS STRAIGHT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9248 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:27-Bit, 2.5MHz to 42MHz DC-Balanced LVDS Deserializers |

| MAX9248ECM/V+ | 功能描述:串行器/解串器 - Serdes 27Bit 2.5-42MHz DC Bl LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9248ECM/V+T | 功能描述:串行器/解串器 - Serdes 27Bit 2.5-42MHz DC Bl LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9248ECM+ | 功能描述:串行器/解串器 - Serdes 27Bit 2.5-42MHz DC Bl LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9248ECM+T | 功能描述:串行器/解串器 - Serdes 27Bit 2.5-42MHz DC Bl LVDS Deserializer RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

发布紧急采购,3分钟左右您将得到回复。