- 您现在的位置:买卖IC网 > PDF目录8575 > MAX9586AZK+T (Maxim Integrated Products)IC AMP VIDEO FILTER TSOT23-5 PDF资料下载

参数资料

| 型号: | MAX9586AZK+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 12/19页 |

| 文件大小: | 0K |

| 描述: | IC AMP VIDEO FILTER TSOT23-5 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 应用: | 重构滤波器 |

| 电路数: | 1 |

| 电流 - 电源: | 4.25mA |

| 电流 - 输出 / 通道: | 140mA |

| 电压 - 电源,单路/双路(±): | 2.7 V ~ 3.6 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | SOT-23-5 细型,TSOT-23-5 |

| 供应商设备封装: | TSOT-23-5 |

| 包装: | 标准包装 |

| 产品目录页面: | 1392 (CN2011-ZH PDF) |

| 其它名称: | MAX9586AZK+TDKR |

MAX9586–MAX9589

Single, Dual, Triple, and Quad Standard-Definition

Video Filter Amplifiers with AC-Coupled Input Buffers

2

_______________________________________________________________________________________

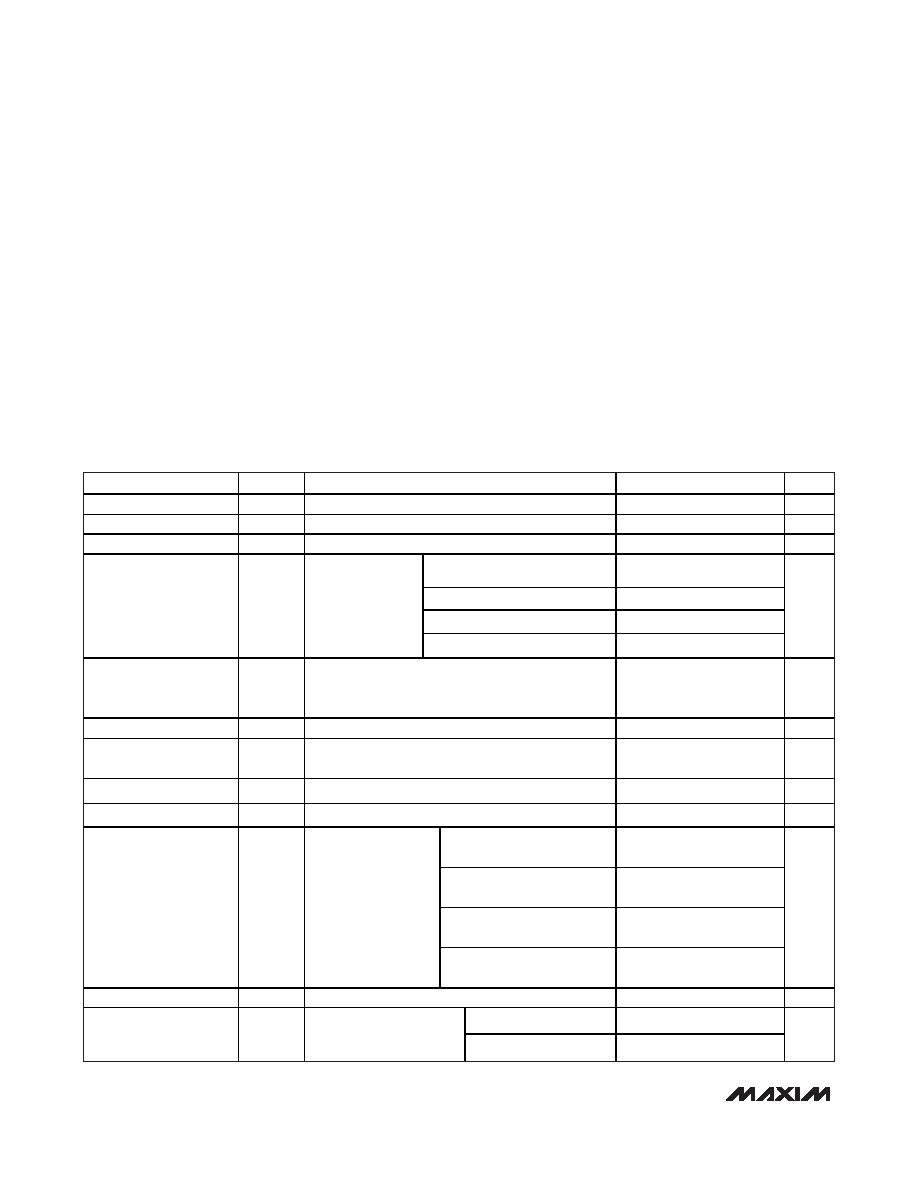

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

(VDD = 3.3V, VGND = 0V, VRL = no load, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

VDD to GND ..............................................................-0.3V to +4V

IN_ to GND ...............................................................-0.3V to +4V

SHDN to GND...........................................................-0.3V to +4V

OUT_ Short Circuit Duration to VDD, GND .................Continuous

Continuous Input Current

IN_, SHDN ....................................................................±20mA

Continuous Power Dissipation (TA = +70°C)

5-Pin Thin SOT23 (derate 9.1mW/°C above +70°C) ....727mW

6-Pin Thin SOT23 (derate 9.1mW/°C above +70°C) ....727mW

8-Pin MAX (derate 4.5mW/°C above +70°C) .............362mW

10-Pin MAX (derate 5.6mW/°C above +70°C) ...........444mW

Operating Temperature Range .........................-40°C to +125°C

Junction Temperature ......................................................+150°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

Soldering Temperature (reflow) .......................................+260°C

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Supply Voltage Range

VDD

Guaranteed by PSRR

2.7

3.6

V

Supply Current

IDD

Per channel

4.25

8

mA

Sync-Tip Clamp Level

VCLP

Sync-tip clamp

0.24

0.41

V

VDD = 2.7V, sync-tip clamp

input

1.05

VDD = 2.7V, bias input

1.05

VDD = 3V, sync-tip clamp input

1.2

Input Voltage Range

VIN

Guaranteed by DC

voltage gain

VDD = 3V, bias input

1.2

VP-P

Sync Crush

Sync-tip clamp, percentage reduction in sync pulse

(0.3VP-P), guaranteed by input clamping current

measurement, measured at input

2%

Input Clamping Current

Sync-tip clamp

1

2

A

Maximum Input Source

Resistance

300

Ω

Bias Voltage

VBIAS

Bias circuit

0.40

0.50

0.62

V

Input Resistance

Bias circuit

11

k

Ω

VDD = 2.7V, VIN = VCLP to

(VCLP + 1.05V)

1.95

2.00

2.04

VDD = 3V, VIN = VCLP to

(VCLP + 1.2V)

1.95

2.00

2.04

VDD = 2.7V, VIN = VBIAS

±0.525V

1.95

2.00

2.04

DC Voltage Gain (Note 2)

AV

RL = 150

Ω to GND

VDD = 3V, VIN = VBIAS

±0.600V

1.95

2.00

2.04

V/V

DC Gain Matching

Guaranteed by DC voltage gain

-2

0

+2

%

Sync-tip clamp

0.2

0.3

0.4

Output Level

Measured at VOUT,

IN_ = 0.1F to GND,

RL = 150

Ω to GND

Bias circuit

1.3

V

相关PDF资料 |

PDF描述 |

|---|---|

| AD7837AR | IC DAC 12BIT DUAL MULT 24-SOIC |

| VE-B6W-MY-B1 | CONVERTER MOD DC/DC 5.5V 50W |

| VE-B1B-MU | CONVERTER MOD DC/DC 95V 200W |

| VE-2NM-IV-F2 | CONVERTER MOD DC/DC 10V 150W |

| VE-B6V-MY-B1 | CONVERTER MOD DC/DC 5.8V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9586EVKIT+ | 功能描述:视频放大器 MAX9586 Evaluation Kit RoHS:否 制造商:ON Semiconductor 通道数量:4 电源类型: 工作电源电压:3.3 V, 5 V 电源电流: 最小工作温度: 最大工作温度: 封装 / 箱体:TSSOP-14 封装:Reel |

| MAX9587AZT+ | 制造商:Maxim Integrated Products 功能描述:SINGLE, DUAL, TRIPLE, AND QUAD STANDARD-DEFINITION VIDEO FIL - Rail/Tube |

| MAX9587AZT+T | 功能描述:视频放大器 Standard-Definition Video Filter Amp RoHS:否 制造商:ON Semiconductor 通道数量:4 电源类型: 工作电源电压:3.3 V, 5 V 电源电流: 最小工作温度: 最大工作温度: 封装 / 箱体:TSSOP-14 封装:Reel |

| MAX9587EVKIT+ | 制造商:Maxim Integrated Products 功能描述:MAX9587 EVAL KIT - Rail/Tube |

| MAX9588AUA+ | 功能描述:视频放大器 Standard-Definition Video Filter Amp RoHS:否 制造商:ON Semiconductor 通道数量:4 电源类型: 工作电源电压:3.3 V, 5 V 电源电流: 最小工作温度: 最大工作温度: 封装 / 箱体:TSSOP-14 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。