- 您现在的位置:买卖IC网 > PDF目录2092 > MAX9888EWY+T (Maxim Integrated Products)IC CODEC AUDIO FLEXSOUND 63WLP PDF资料下载

参数资料

| 型号: | MAX9888EWY+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 85/115页 |

| 文件大小: | 0K |

| 描述: | IC CODEC AUDIO FLEXSOUND 63WLP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 系列: | DirectDrive®, FLEXSOUND™ |

| 类型: | D 类 |

| 输出类型: | 3 通道,带立体声耳机 |

| 在某负载时最大输出功率 x 通道数量: | 1.37W x 2 @ 8 欧姆; 40mW x 2 @ 16 欧姆 |

| 电源电压: | 2.8 V ~ 5.5 V |

| 特点: | 消除爆音,差分输入,I²S,麦克风,静音,关机 |

| 安装类型: | 表面贴装 |

| 供应商设备封装: | 63-WLP |

| 封装/外壳: | 63-WFBGA,WLCSP |

| 包装: | 带卷 (TR) |

| 配用: | MAX9888EVKIT+-ND - KIT EVALUATION FOR MAX9888 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页当前第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页

Stereo Audio CODEC

with FlexSound Technology

MAX9888

71

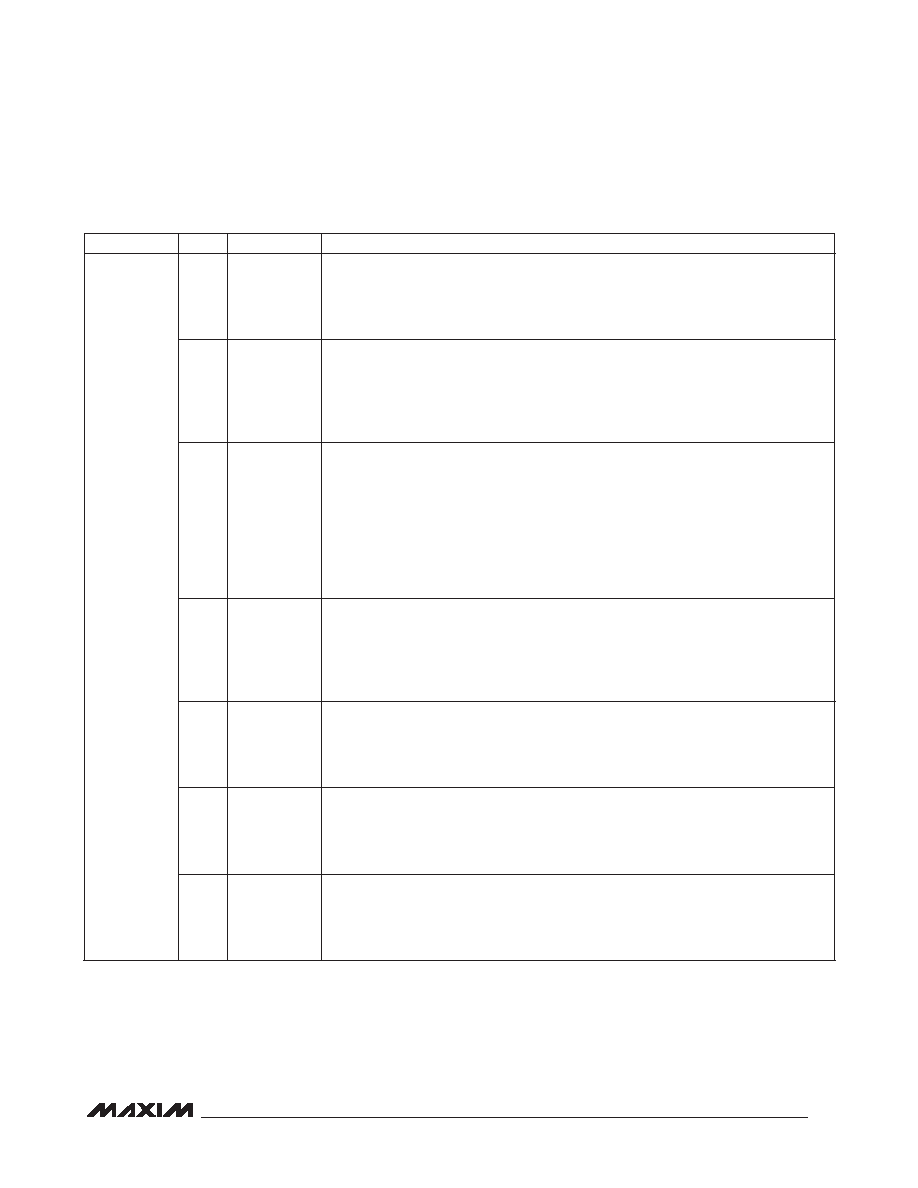

Table 10. Digital Audio Interface Registers

REGISTER

BIT

NAME

DESCRIPTION

0x14/0x1C

7

MAS1/MAS2

DAI1/DAI2 Master Mode

In master mode, DAI1/DAI2 outputs LRCLK and BCLK. In slave mode, DAI1/DAI2

accept LRCLK and BCLK as inputs.

0 = Slave mode

1 = Master mode

6

WCI1/WCI2

DAI1/DAI2 Word Clock Invert

TDM1/TDM2 = 0:

0 = Left-channel data is transmitted while LRCLK is low.

1 = Right-channel data is transmitted while LRCLK is low.

TDM1/TDM2 = 1:

Always set WCI = 0.

5

BCI1/BCI2

DAI1/DAI2 Bit Clock Invert

BCI1/BCI2 must be set to 1 when TDM1/TDM2 = 1.

0 = SDIN is accepted on the rising edge of BCLK.

SDOUT is valid on the rising edge of BCLK.

1 = SDIN is accepted on the falling edge of BCLK.

SDOUT is valid on the falling edge of BCLK.

Master Mode:

0 = LRCLK transitions on the falling edge of BCLK.

1 = LRCLK transitions on the rising edge of BCLK.

4

DLY1/DLY2

DAI1/DAI2 Data Delay

DLY1/DLY2 has no effect when TDM1/TDM2 = 1.

0 = The most significant data bit is clocked on the first active BCLK edge after an

LRCLK transition.

1 = The most significant data bit is clocked on the second active BCLK edge after an

LRCLK transition.

2

TDM1/TDM2

DAI1/DAI2 Time-Division Multiplex Mode (TDM Mode)

Set TDM1/TDM2 when communicating with devices that use a frame synchronization

pulse on LRCLK instead of a square wave.

0 = Disabled

1 = Enabled (BCI1/BCI2 must be set to 1)

1

FSW1/FSW2

DAI1/DAI2 Wide Frame Sync Pulse

Increases the width of the frame sync pulse to the full data width when TDM1/TDM2 =

1. FSW1/FSW2 has no effect when TDM1/TDM2 = 0.

0 = Disabled

1 = Enabled

0

WS1/WS2

DAI1/DAI2 Audio Data Bit Depth

Determines the maximum bit depth of audio being transmitted and received. Data is

always 16 bit when TDM1/TMD2 = 0.

0 = 16 bits

1 = 24 bits

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9890AEBL+T | IC SUPP CLICK-POP 9-UCSP |

| MAX9892ELT+T | IC ELIMINATOR CLICK/POP 6UDFN |

| MAX995EUD+ | IC COMPARATOR R-R 14-TSSOP |

| MAX9967ADCCQ+D | IC DCL DUAL 500MBPS ATE 100TQFP |

| MAX998EUT-T | IC COMP SNGL HI-SPEED LP SOT23-6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9889EWO+T | 功能描述:接口—CODEC RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| MAX988ESA | 功能描述:校验器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

| MAX988ESA+ | 功能描述:校验器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

| MAX988ESA+T | 功能描述:校验器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

| MAX988ESA-T | 功能描述:校验器 IC Single uPower Comparator RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。