- 您现在的位置:买卖IC网 > PDF目录80562 > MB95F116MSPMC 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PQFP52 PDF资料下载

参数资料

| 型号: | MB95F116MSPMC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PQFP52 |

| 封装: | 10 X 10 MM, 1.70 MM HEIGHT, 0.65 MM PITCH, PLASTIC, LQFP-52 |

| 文件页数: | 15/76页 |

| 文件大小: | 1313K |

| 代理商: | MB95F116MSPMC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

MB95110M Series

22

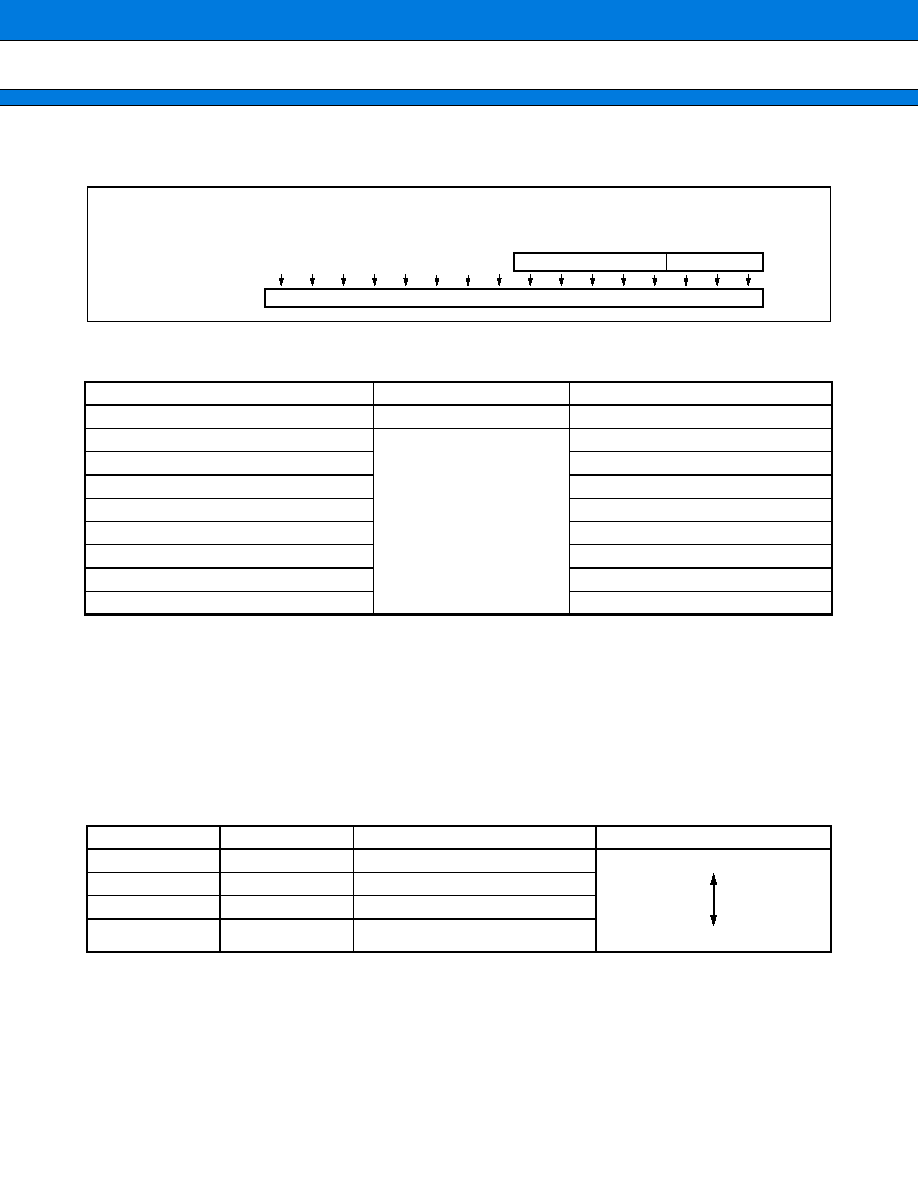

The RP indicates the address of the register bank currently being used. The relationship between the content

of RP and the real address conforms to the conversion rule illustrated below:

The DP specifies the area for mapping instructions (16 different instructions such as MOV A, dir) using direct

addresses to 0080H to 00FFH.

The CCR consists of the bits indicating arithmetic operation results or transfer data contents and the bits that

control CPU operations at interrupt.

Direct bank pointer (DP2 to DP0)

Specified address area

Mapping area

XXXB (no effect to mapping)

0000H to 007FH

0000H to 007FH (without mapping)

000B (initial value)

0080H to 00FFH

0080H to 00FFH (without mapping)

001B

0100H to 017FH

010B

0180H to 01FFH

011B

0200H to 027FH

100B

0280H to 02FFH

101B

0300H to 037FH

110B

0380H to 03FFH

111B

0400H to 047FH

H flag

: Set to “1” when a carry or a borrow from bit 3 to bit 4 occurs as a result of an arithmetic operation.

Cleared to “0” otherwise. This flag is for decimal adjustment instructions.

I flag

: Interrupt is enabled when this flag is set to “1”. Interrupt is disabled when this flag is set to “0”.

The flag is set to “0” when reset.

IL1, IL0 : Indicates the level of the interrupt currently enabled. Processes an interrupt only if its request level

is higher than the value indicated by these bits.

IL1

IL0

Interrupt level

Priority

00

0

High

Low ( no interruption)

01

1

10

2

11

3

N flag

: Set to “1” if the MSB is set to “1” as the result of an arithmetic operation. Cleared to “0” when the

bit is set to “0”.

Z flag

: Set to “1” when an arithmetic operation results in “0”. Cleared to “0” otherwise.

V flag

: Set to “1” if the complement on 2 overflows as a result of an arithmetic operation. Cleared to “0”

otherwise.

C flag

: Set to “1” when a carry or a borrow from bit 7 occurs as a result of an arithmetic operation. Cleared

to “0” otherwise. Set to the shift-out value in the case of a shift instruction.

"0"

"1"

R4

R3

R2

R1

R0

b2

b1

b0

A7

A6

A5

A4

A3

A2

A1

A0

A15 A14 A13 A12 A11 A10

A9

A8

Rule for Conversion of Actual Addresses in the General-purpose Register Area

Generated address

RP upper

OP code lower

相关PDF资料 |

PDF描述 |

|---|---|

| MSP430F2418TZQW | 16-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PBGA113 |

| MPC8547HXAUJ | 32-BIT, 1000 MHz, MICROPROCESSOR, CBGA783 |

| MSM63188A-XXX | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, UUC159 |

| M30260F8BGP | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP48 |

| M30281FAHP-D9 | 16-BIT, FLASH, 20 MHz, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB95F116MW | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontrollers |

| MB95F116MW/F116NW | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontrollers |

| MB95F116MWPMC | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Microcontrollers |

| MB95F116NS | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontrollers |

| MB95F116NSPMC | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Microcontrollers |

发布紧急采购,3分钟左右您将得到回复。