- 您现在的位置:买卖IC网 > PDF目录80578 > MB95R203PF-G-NE2 (FUJITSU LTD) 8-BIT, 10 MHz, MICROCONTROLLER, PDSO20 PDF资料下载

参数资料

| 型号: | MB95R203PF-G-NE2 |

| 厂商: | FUJITSU LTD |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 10 MHz, MICROCONTROLLER, PDSO20 |

| 封装: | 7.5 MM X 12.7 MM, 2.65 MM HEIGHT, 1.27 MM PITCH, PLASTIC, SOP-20 |

| 文件页数: | 31/56页 |

| 文件大小: | 1925K |

| 代理商: | MB95R203PF-G-NE2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

MB95R203

DS07-12625-3E

37

(Continued)

(Vcc

= 3.3 V, Vss = 0.0 V, TA = 20 °C to +70 °C)

*1 : R, C : Pull-up resistance and load capacitance of the SCL and SDA lines.

*2 :

Refer to “ (2) Source Clock/Machine Clock” for details on tMCLK.

m is the CS4 and CS3 bits (bit 4 and bit 3) of the I2C clock control register (ICCR0) .

n is the CS2 to CS0 bits (bit 2 to bit0) of the I2C clock control register (ICCR0) .

The actual I2C timing is determined by the machine (tMCLK) and the values of m and n configured in bits

CS4 to CS0 of the I2C clock control register (ICCR0) .

Standard-mode :

m and n can be set in the range : 0.9 MHz < tMCLK (machine clock) < 10 MHz.

The machine clock to be used is determined by the settings of m and n as follows.

(m, n)

= (1, 8)

: 0.9 MHz < tMCLK

≤ 1 MHz

(m, n)

= (1, 22) , (5, 4) , (6, 4) , (7, 4) , (8, 4)

: 0.9 MHz < tMCLK

≤ 2 MHz

(m, n)

= (1, 38) , (5, 8) , (6, 8) , (7, 8) , (8, 8)

: 0.9 MHz < tMCLK

≤ 4 MHz

(m, n)

= (1, 98)

: 0.9 MHz < tMCLK

≤ 1 MHz

Fast-mode :

m and n can be set in the range : 3.3 MHz < tMCLK (machine clock) < 10 MHz.

The machine clock to be used is determined by the settings of m and n as follows.

(m, n)

= (1, 8)

: 3.3 MHz < tMCLK

≤ 4 MHz

(m, n)

= (1, 22) , (5, 4)

: 3.3 MHz < tMCLK

≤ 8 MHz

(m, n)

= (6, 4)

: 3.3 MHz < tMCLK

≤ 10 MHz

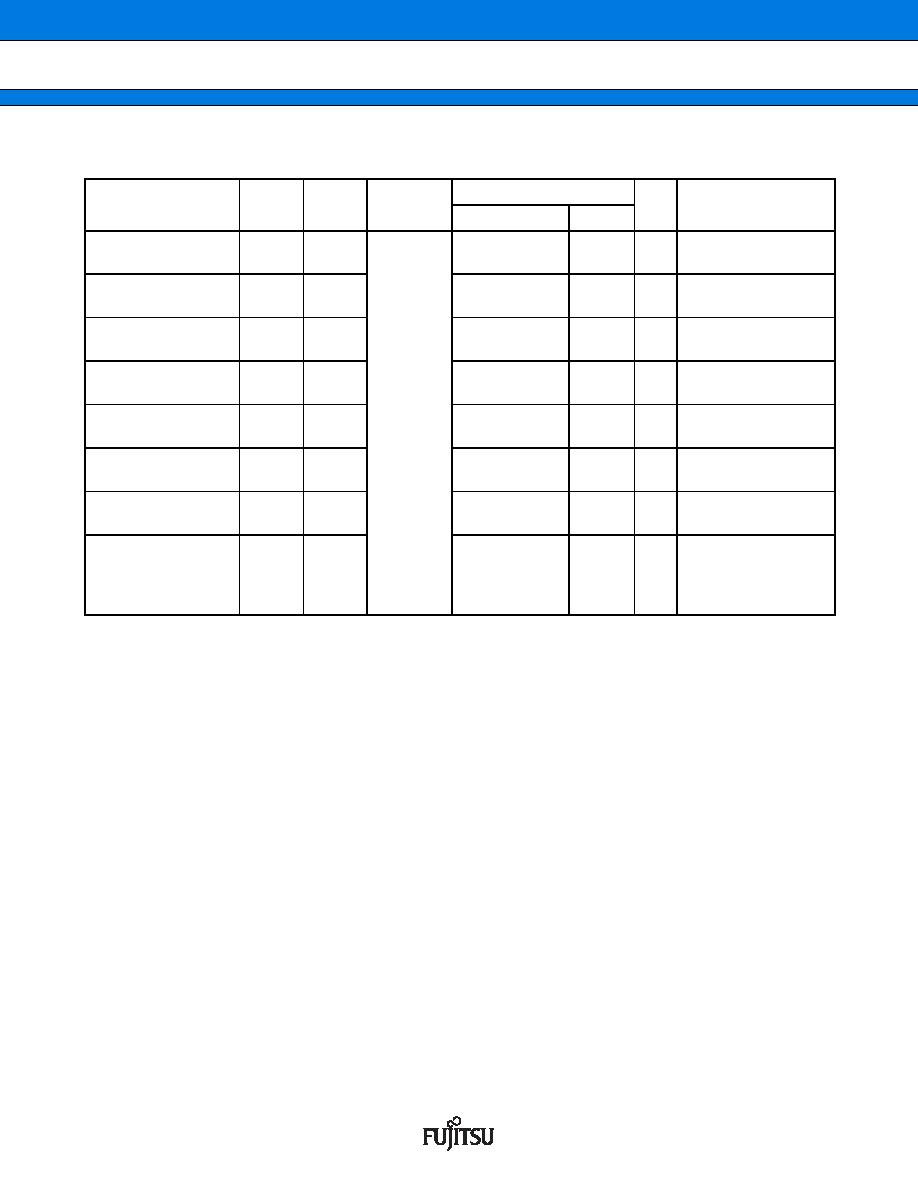

Parameter

Symbol

Pin

name

Condi-

tions

Value*2

Unit

Remarks

Min

Max

Stop condition

detection

tSU;STO

SCL

SDA

R

= 1.7 kΩ,

C

= 50 pF*1

4 tMCLK

20

ns

Undetected when 1 tM-

CLK

is used at reception

Restart condition

detection condition

tSU;STA

SCL

SDA

2 tMCLK

20

ns

Undetected when 1 tM-

CLK

is used at reception

Bus free time

tBUF

SCL

SDA

2 tMCLK

20

ns

During reception

Data hold time

tHD;DAT

SCL

SDA

2 tMCLK

20

ns

In slave transmission

mode

Data setup time

tSU;DAT

SCL

SDA

tLOW

3 tMCLK

20

ns

In slave transmission

mode

Data hold time

tHD;DAT

SCL

SDA

0

ns

During reception

Data setup time

tSU;DAT

SCL

SDA

tMCLK

20

ns

During reception

SDA

↓ → SCL ↑

(when using wakeup

function)

tWAKEUP

SCL

SDA

Oscillation sta-

bilization wait

time

+ 2 tMCLK

20

ns

相关PDF资料 |

PDF描述 |

|---|---|

| MAC7121CAG40 | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP112 |

| MC68060FE50 | 32-BIT, 50 MHz, MICROPROCESSOR, CQFP208 |

| MB88152APNF-G-100-JN-EFE1 | 16.6 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| MK53N512CLQ100R | FLASH, 100 MHz, RISC MICROCONTROLLER, PQFP144 |

| MC3S12XEP100J1CAG | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB95R203P-G-SH-JNE2 | 制造商:FUJITSU 功能描述:IC MCU 8BIT 8FX 8K FRAM 24SDIP |

| MB96300 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:16-bit Proprietary Microcontroller |

| MB96310 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:16-bit Proprietary Microcontroller |

| MB96320 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:16-bit Proprietary Microcontroller |

| MB96330 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:16-bit Proprietary Microcontroller |

发布紧急采购,3分钟左右您将得到回复。