- 您现在的位置:买卖IC网 > PDF目录371001 > MC-80C32E-30-E (ATMEL CORP) Rad. Tolerant 8-bit ROMless Microcontroller PDF资料下载

参数资料

| 型号: | MC-80C32E-30-E |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | Rad. Tolerant 8-bit ROMless Microcontroller |

| 中文描述: | 8-BIT, 30 MHz, MICROCONTROLLER, CDIP40 |

| 封装: | 0.600 INCH, SIDE BRAZED, DIP-40 |

| 文件页数: | 6/20页 |

| 文件大小: | 298K |

| 代理商: | MC-80C32E-30-E |

6

80C32E

4149M–AERO–06/04

Idle Mode

An instruction that sets PCON.0 causes that to be the last instruction executed before

going into Idle mode. In Idle mode, the internal clock signal is gated off to the CPU, but

not to the interrupt, Timer, and Serial Port functions. The CPU status is preserved in its

entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator, RAM

and all other registers maintain their data during Idle. The port pins hold the logical

states they had at the time Idle was activated. ALE and PSEN hold at logic high levels.

There are two ways to terminate the Idle. Activation of any enabled interrupt will cause

PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be ser-

viced, and following RETI the next instruction to be executed will be the one following

the instruction that put the device into idle.

The flag bits GF0 and GF1 can be used to give an indication if an interrupt occurred dur-

ing normal operation or during an Idle. For example, an instruction that activates Idle

can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt

service routine can examine the flag bits.

The other way of terminating the Idle mode is with a hardware reset. Since the clock

oscillator is still running, the hardware reset needs to be held active for only two

machine cycles (24 oscillator periods) to complete the reset.

Power-down Mode

To save maximum power, a power-down mode can be invoked by software.

In power-down mode, the oscillator is stopped and the instruction that invoked power-

down mode is the last instruction executed. The internal RAM and SFRs retain their

value until the power-down mode is terminated. V

CC

can be lowered to save further

power. Either a hardware reset or an external interrupt can cause an exit from power-

down. To properly terminate power-down, the reset or external interrupt should not be

executed before V

CC

is restored to its normal operating level and must be held active

long enough for the oscillator to restart and stabilize.

Only external interrupts INT0 and INT1 are useful to exit from power-down. For that,

interrupt must be enabled and configured as level or edge sensitive interrupt input.

Holding the pin low restarts the oscillator but bringing the pin high completes the exit as

detailed in Figure 1. When both interrupts are enabled, the oscillator restarts as soon as

one of the two inputs is held low and Power-down exit will be completed when the first

input will be released. In this case the higher priority interrupt service routine is executed

Once the interrupt is serviced, the next instruction to be executed after RETI will be the

one following the instruction that put 80C32E into power-down mode.

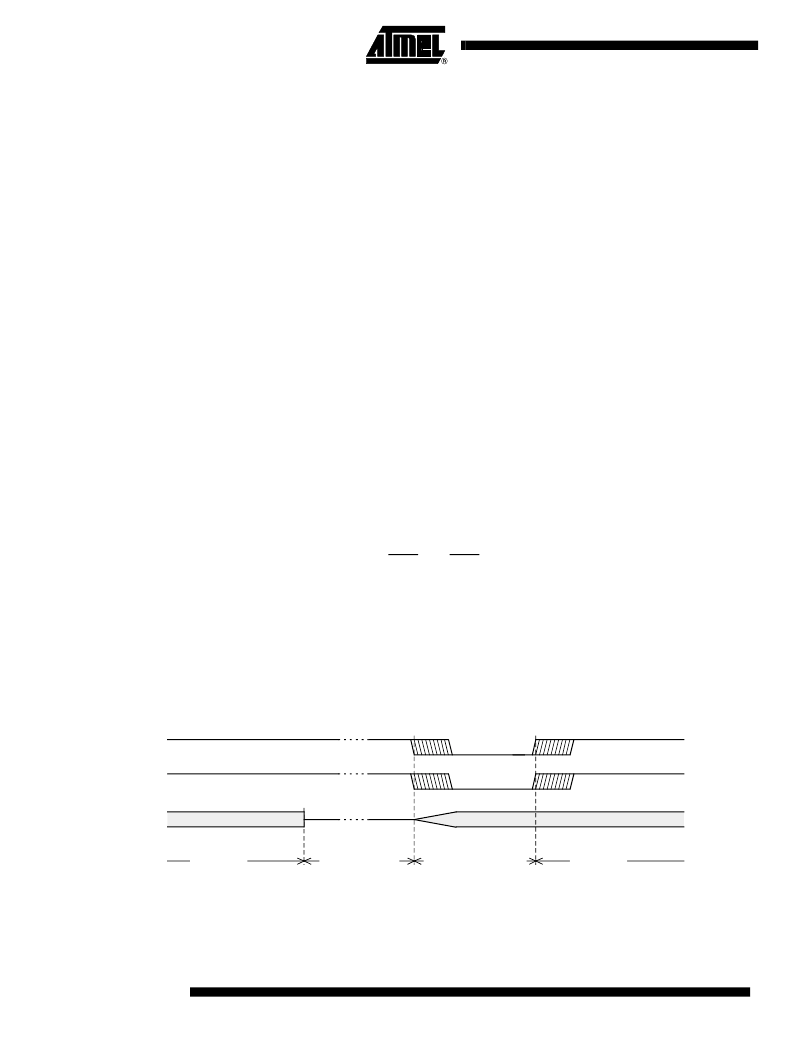

Figure 1.

Power-down Exit Waveform

Exit from power-down by reset redefines all the SFRs, exit from power-down by external

interrupt does no affect the SFRs.

INT1

INT0

XTAL1

Power-down phase

Oscillator restart phase

Active phase

Active phase

相关PDF资料 |

PDF描述 |

|---|---|

| MC100E211FN | 1:6 DIFFERENTIAL CLOCK DISTRIBUTION CHIP |

| MC10E211 | Replaced by TPS2055A : 0.345A, 2.7-5.5V Single Hi-Side MOSFET, Fault Report, Act-High Enable 8-PDIP -40 to 85 |

| MC10E211FN | 1:6 DIFFERENTIAL CLOCK DISTRIBUTION CHIP |

| MC100EP111 | Low-Voltage 1:10 Differential ECL/PECL/HSTL Clock Driver(低压1:10差分ECL/PECL/HSTL时钟驱动器) |

| MC100H603FN | 9-Bit Latch ECL/TTL Translator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC80D21000G | 制造商:COR 功能描述:RN |

| MC80F0104 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0104B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0104D | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0204 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

发布紧急采购,3分钟左右您将得到回复。