- 您现在的位置:买卖IC网 > PDF目录80481 > MC8641VU1500KE (FREESCALE SEMICONDUCTOR INC) 32-BIT, 166.66 MHz, MICROPROCESSOR, CBGA1023 PDF资料下载

参数资料

| 型号: | MC8641VU1500KE |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 166.66 MHz, MICROPROCESSOR, CBGA1023 |

| 封装: | 33 X 33 MM, ROHS COMPLIANT, CERAMIC, BGA-1023 |

| 文件页数: | 8/130页 |

| 文件大小: | 1493K |

| 代理商: | MC8641VU1500KE |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页

MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications, Rev. 2

Freescale Semiconductor

105

Clocking

18 Clocking

This section describes the PLL configuration of the MPC8641. Note that the platform clock is identical to

the MPX clock.

18.1

Clock Ranges

Table 64 provides the clocking specifications for the processor cores and Table 65 provides the clocking

specifications for the memory bus. Table 66 provides the clocking for the Platform/MPX bus and Table 67

provides the clocking for the Local bus.

37.This pin is only an output in FIFO mode when used as Rx Flow Control.

38.This pin functions as cfg_dram_type[0 or 1] at reset and MUST BE VALID BEFORE HRESET ASSERTION in device sleep

mode.

39. Should be pulled to ground if unused (such as in FIFO, MII and RMII modes).

40. See Section 18.4.2, “Platform to FIFO Restrictions” for clock speed limitations for this pin when used in FIFO mode.

41. The phase between the output clocks TSEC1_GTX_CLK and TSEC2_GTX_CLK (ports 1 and 2) is no more than 100 ps.

The phase between the output clocks TSEC3_GTX_CLK and TSEC4_GTX_CLK (ports 3 and 4) is no more than 100 ps.

42. For systems which boot from Local Bus (GPCM)-controlled flash, a pullup on LGPL4 is required.

Special Notes for Single Core Device:

S1. Solder ball for this signal will not be populated in the single core package.

S2. The PLL filter from VDD_Core1 to AVDD_Core1 should be removed. AVDD_Core1 should be pulled to ground with a weak

(2–10 k

Ω) resistor. See Section 20.2.1, “PLL Power Supply Filtering” for more details.

S3. This pin should be pulled to GND for the single core device.

S4. No special requirement for this pin on single core device. Pin should be tied to power supply as directed for dual core.

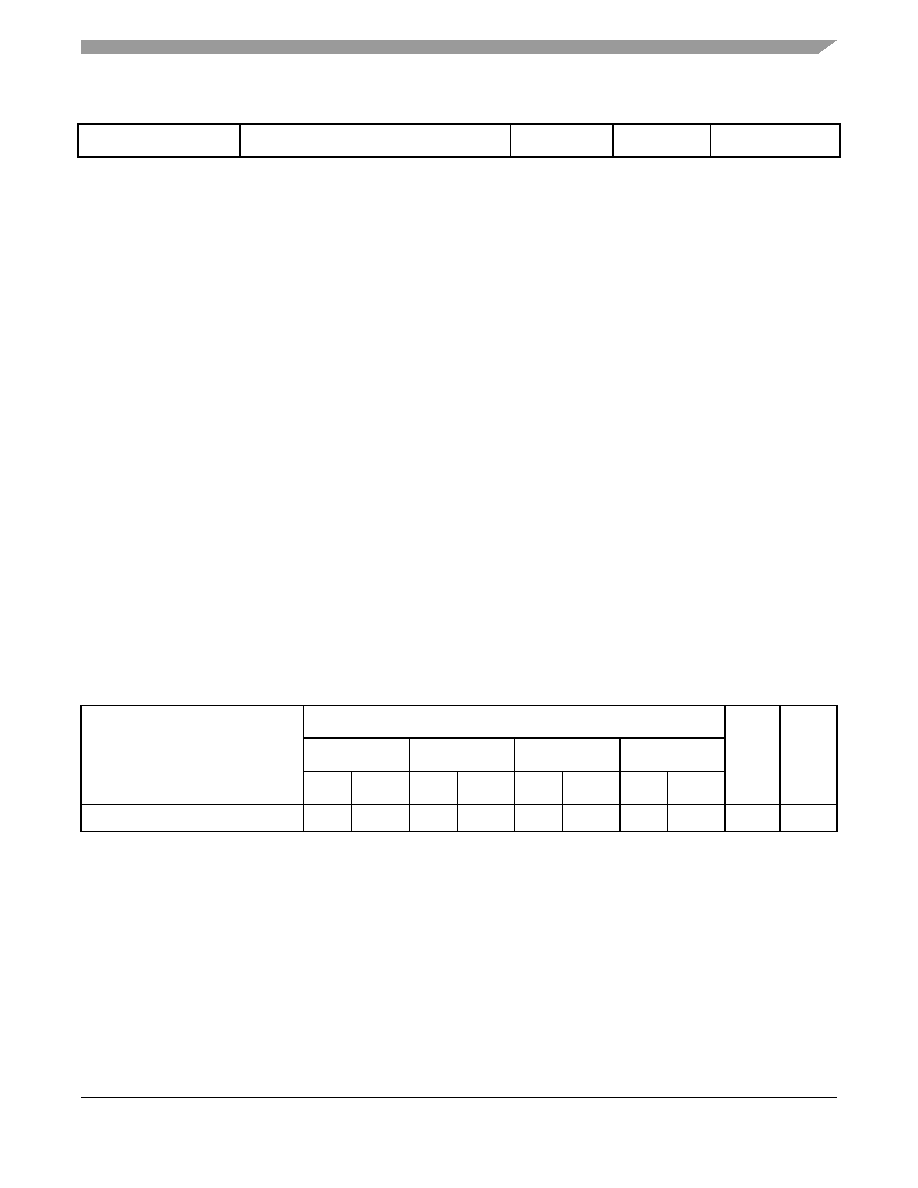

Table 64. Processor Core Clocking Specifications

Characteristic

Maximum Processor Core Frequency

Unit

Notes

1000 MHz

1250MHz

1333MHz

1500 MHz

Min

Max

Min

Max

Min

Max

Min

Max

e600 core processor frequency

800

1000

800

1250

800

1333

800

1500

MHz

1, 2

Notes:

1. Caution: The MPX clock to SYSCLK ratio and e600 core to MPX clock ratio settings must be chosen such that the resulting

SYSCLK frequency, e600 (core) frequency, and MPX clock frequency do not exceed their respective maximum or minimum

operating frequencies. Refer to Section 18.2, “MPX to SYSCLK PLL Ratio,” and Section 18.3, “e600 to MPX clock PLL Ratio,”

for ratio settings.

2. The minimum e600 core frequency is based on the minimum platform clock frequency of 400 MHz.

Table 63. MPC8641 Signal Reference by Functional Block (continued)

Name1

Package Pin Number

Pin Type

Power Supply

Notes

相关PDF资料 |

PDF描述 |

|---|---|

| MC9S08EL16VTLR | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDSO28 |

| MC9S08EL32VTJR | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDSO20 |

| MC68HRC08JK3EMDW | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 |

| MCL908QT4CP | 8-BIT, FLASH, 2 MHz, MICROCONTROLLER, PDIP8 |

| MC68HSC05C4P | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDIP40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC8641VU1500N | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Integrated Host Processor Hardware Specifications |

| MC867P | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

| MC8704_1101297 | 制造商:Sierra Wireless 功能描述:3G MINI CARD 制造商:Sierra Wireless 功能描述:MC8704_1101297 |

| MC8704_1101443 | 制造商:Sierra Wireless 功能描述:INTEGRATED RADIO / M2M UNIT |

| MC8705 | 制造商:SIERRA WIRELESS 功能描述:MINICARD 3G 4BAND HSPA+21 GPS 制造商:SIERRA WIRELESS 功能描述:MODULE, HSPA, GPS, MDM8200A, 3G, USB 制造商:SIERRA WIRELESS 功能描述:MODULE, HSPA, GPS, MDM8200A, 3G, USB; Frequency RF:2.1MHz; Module Interface:USB ;RoHS Compliant: Yes |

发布紧急采购,3分钟左右您将得到回复。