- 您现在的位置:买卖IC网 > PDF目录80530 > MC9328MXLDVH15 (MOTOROLA INC) 150 MHz, RISC PROCESSOR, PBGA256 PDF资料下载

参数资料

| 型号: | MC9328MXLDVH15 |

| 厂商: | MOTOROLA INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 150 MHz, RISC PROCESSOR, PBGA256 |

| 封装: | 14 X 14 MM, 1.30 MM HEIGHT, 0.80 MM PITCH, MAPBGA-256 |

| 文件页数: | 52/89页 |

| 文件大小: | 1869K |

| 代理商: | MC9328MXLDVH15 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页当前第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

56

MC9328MXL Advance Information

MOTOROLA

Specifications

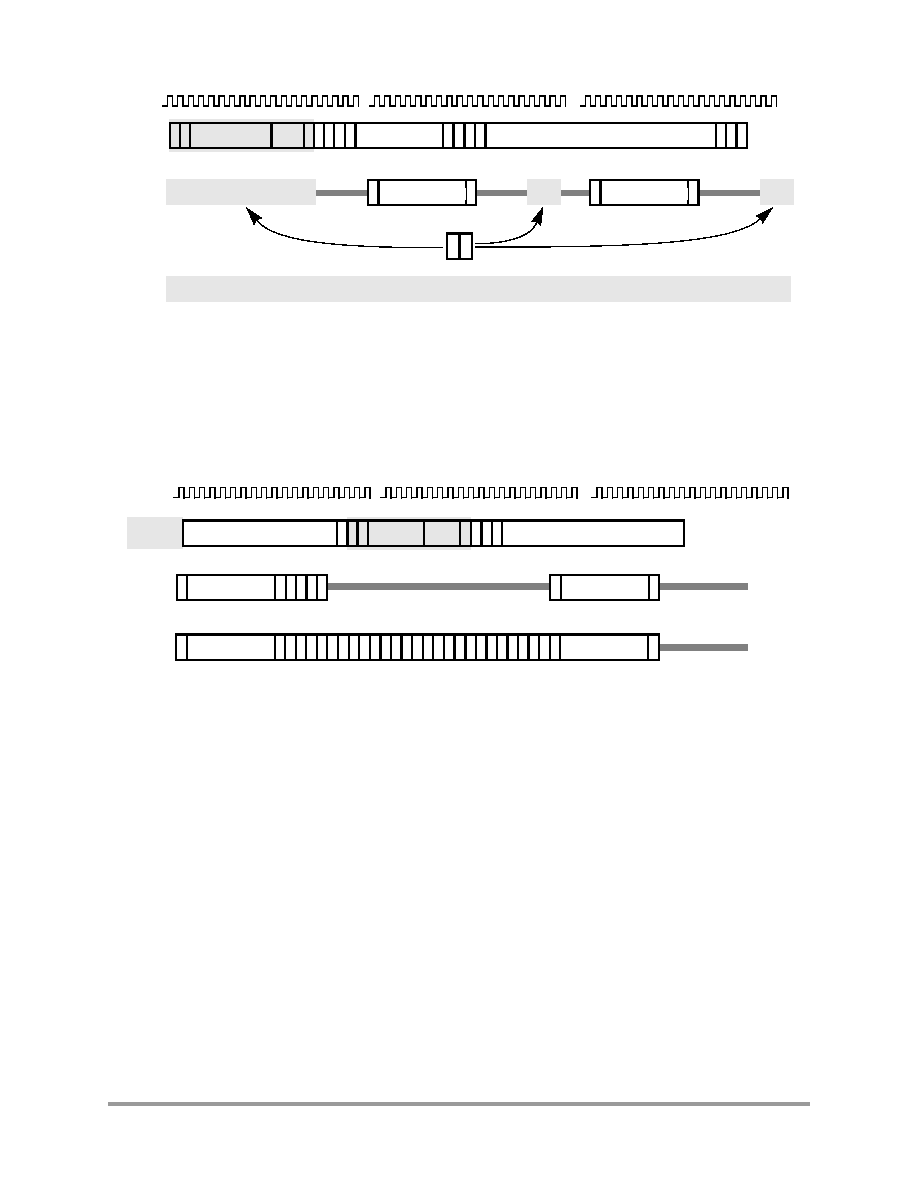

Figure 44. SDIO IRQ Timing Diagram

ReadWait is another feature in SDIO that allows the user to submit commands during the data transfer. In

this mode, the block temporarily pauses the data transfer operation counter and related status, yet keeps the

clock running, and allows the user to submit commands as normal. After all commands are submitted, the

user can switch back to the data transfer operation and all counter and status values are resumed as access

continues.

Figure 45. SDIO ReadWait Timing Diagram

3.12 Memory Stick Host Controller

The Memory Stick protocol requires three interface signal line connections for data transfers: MS_BS,

MS_SDIO, and MS_SCLKO. Communication is always initiated by the MSHC and operates the bus in

either four-state or two-state access mode.

The MS_BS signal classifies data on the SDIO into one of four states (BS0, BS1, BS2, or BS3) according

to its attribute and transfer direction. BS0 is the INT transfer state, and during this state no packet

transmissions occur. During the BS1, BS2, and BS3 states, packet communications are executed. The BS1,

BS2, and BS3 states are regarded as one packet length and one communication transfer is always

completed within one packet length (in four-state access mode).

The Memory Stick usually operates in four state access mode and in BS1, BS2, and BS3 bus states. When

an error occurs during packet communication, the mode is shifted to two-state access mode, and the BS0

and BS1 bus states are automatically repeated to avoid a bus collision on the SDIO.

Interrupt Period

IRQ

DAT[1]

For 4-bit

L H

Interrupt Period

DAT[1]

For 1-bit

CMD

Content

S T

E Z Z P

E Z Z

******

Z Z

Response

CRC

S

Z

E

S

Block Data

E

S

Block Data

DAT[1]

For 4-bit

DAT[2]

For 4-bit

CMD

******

P S T

E Z Z

******

CMD52

Z

CRC

E Z Z

S

Block Data

L L L L L L L L L L L L L L L L L L L L L H Z S

E

S

Block Data

E

Block Data

Z Z L H

E

S

Block Data

相关PDF资料 |

PDF描述 |

|---|---|

| MC9SDJ128BCFUR2 | 16-BIT, FLASH, 25 MHz, MICROCONTROLLER, PQFP80 |

| MC9S08SG16JTJR | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PDSO20 |

| MC68HC11E0CFU3R2 | 8-BIT, 3 MHz, MICROCONTROLLER, PQFP64 |

| MC68HC11E0CPB3 | 8-BIT, 3 MHz, MICROCONTROLLER, PQFP52 |

| ML9042-21CVWA | 17 X 100 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC233 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC9328MXLDVH20 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:i.MX Integrated Portable System Processor |

| MC9328MXLDVM15 | 功能描述:处理器 - 专门应用 DRAGONBALL CORSICA PB-FR RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MC9328MXLDVM15R2 | 功能描述:处理器 - 专门应用 DRAGONBALL CORSICA PB-FR RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MC9328MXLDVM20 | 功能描述:处理器 - 专门应用 DRAGONBALL CORSICA PB-FR RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MC9328MXLDVM20R2 | 功能描述:处理器 - 专门应用 DRAGONBALL CORSICA PB-FR RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

发布紧急采购,3分钟左右您将得到回复。