- 您现在的位置:买卖IC网 > PDF目录17100 > MCP355XDM-TAS (Microchip Technology)BOARD DEMO TINY APP SNSR MCP355X PDF资料下载

参数资料

| 型号: | MCP355XDM-TAS |

| 厂商: | Microchip Technology |

| 文件页数: | 8/36页 |

| 文件大小: | 0K |

| 描述: | BOARD DEMO TINY APP SNSR MCP355X |

| 产品培训模块: | MCP3901 Analog Front End |

| 标准包装: | 1 |

| ADC 的数量: | 1 |

| 位数: | 22 |

| 数据接口: | 串行 |

| 输入范围: | ±3 V |

| 工作温度: | -40°C ~ 125°C |

| 已用 IC / 零件: | MCP355x |

| 已供物品: | 板,CD |

| 产品目录页面: | 672 (CN2011-ZH PDF) |

| 相关产品: | MCP3550T-60E/SN-ND - IC ADC 22BIT 2.7V 1CH 8SOIC MCP3550T-60E/MS-ND - IC ADC 22BIT 2.7V 1CH 8MSOP MCP3550T-50E/SN-ND - IC ADC 22BIT 2.7V 1CH 8SOIC MCP3550T-50E/MS-ND - IC ADC 22BIT 2.7V 1CH 8MSOP MCP3550-60E/SN-ND - IC ADC 22BIT 2.7V 1CH 8SOIC MCP3550-60E/MS-ND - IC ADC 22BIT 2.7V 1CH 8MSOP MCP3550-50E/SN-ND - IC ADC 22BIT 2.7V 1CH 8SOIC MCP3550-50E/MS-ND - IC ADC 22BIT 2.7V 1CH 8MSOP MCP3553T-E/SN-ND - IC ADC 22BIT 2.7V 1CH SPI 8SOIC MCP3553T-E/MS-ND - IC ADC 22BIT 2.7V 1CH SPI 8MSOP 更多... |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

MCP3550/1/3

DS21950E-page 16

2009 Microchip Technology Inc.

4.1

MCP3550/1/3 Delta-Sigma

Modulator with Internal Offset and

Gain Calibration

The converter core of the MCP3550/1/3 devices is a

third-order delta-sigma modulator with automatic gain

and offset error calibrations. The modulator uses a 1-bit

DAC structure. The delta-sigma modulator processes

the sampled charges through switched capacitor

structures controlled by a very low drift oscillator for

reduced clock jitter.

During the conversion process, the modulator outputs

a bit stream with the bit frequency equivalent to the

implemented in the modulator ensures very high

resolution and high averaging factor to achieve low-

noise specifications. The bit stream output of the

modulator is then processed by the digital decimation

filter in order to provide a 22-bit output code at a data

rate of 12.5 Hz for the MCP3550-50, 15 Hz for the

MCP3550-60, 13.75 Hz for the MCP3551 and 60 Hz

for the MCP3553. Since the oversampling ratio is lower

with the MCP3553 device, a much higher output data

rate is achieved while still achieving 20 bits No Missing

Codes (NMC) and 20.6 ENOB.

A self-calibration of offset and gain occurs at the onset

of every conversion. The conversion data available at

the output of the device is always calibrated for offset

and gain through this process. This offset and gain

auto-calibration is performed internally and has no

impact on the speed of the converter since the offset

and gain errors are calibrated in real-time during the

conversion. The real-time offset and gain calibration

schemes do not affect the conversion process.

4.2

Digital Filter

The MCP3550/1/3 devices include a digital decimation

filter, which is a fourth-order modified SINC filter. This

filter averages the incoming bit stream from the

modulator and outputs a 22-bit conversion word in

binary two's complement. When all bits have been

processed by the filter, the output code is ready for SPI

communication, the RDY flag is set on the SDO/RDY

pin and all the internal registers are reset in order to

process the next conversion.

Like the commonly used SINC filter, the modified SINC

filter in the MCP3550/1/3 family has the main notch

frequency located at fS/(OSR*L), where fS is the bit

stream sample frequency. OSR is the Oversampling

Ratio and L is the order of the filter.

The MCP3550-50 device has the main filter notch

located at 50 Hz. For the MCP3550-60 device, the

notch is located at 60 Hz. The MCP3551 device has its

notch located at 55 Hz, and for the MCP3553 device,

the main notch is located at 240 Hz, with an OSR of

128. (see Table 4-1 for rejection performance).

The digital decimation SINC filter has been modified in

order to offer staggered zeros in its transfer function.

This modification is intended to widen the main notch in

order to be less sensitive to oscillator deviation or line-

frequency drift. The MCP3551 filter has staggered

zeros spread in order to reject both 50 Hz and 60 Hz

line frequencies simultaneously (see Figure 4-2).

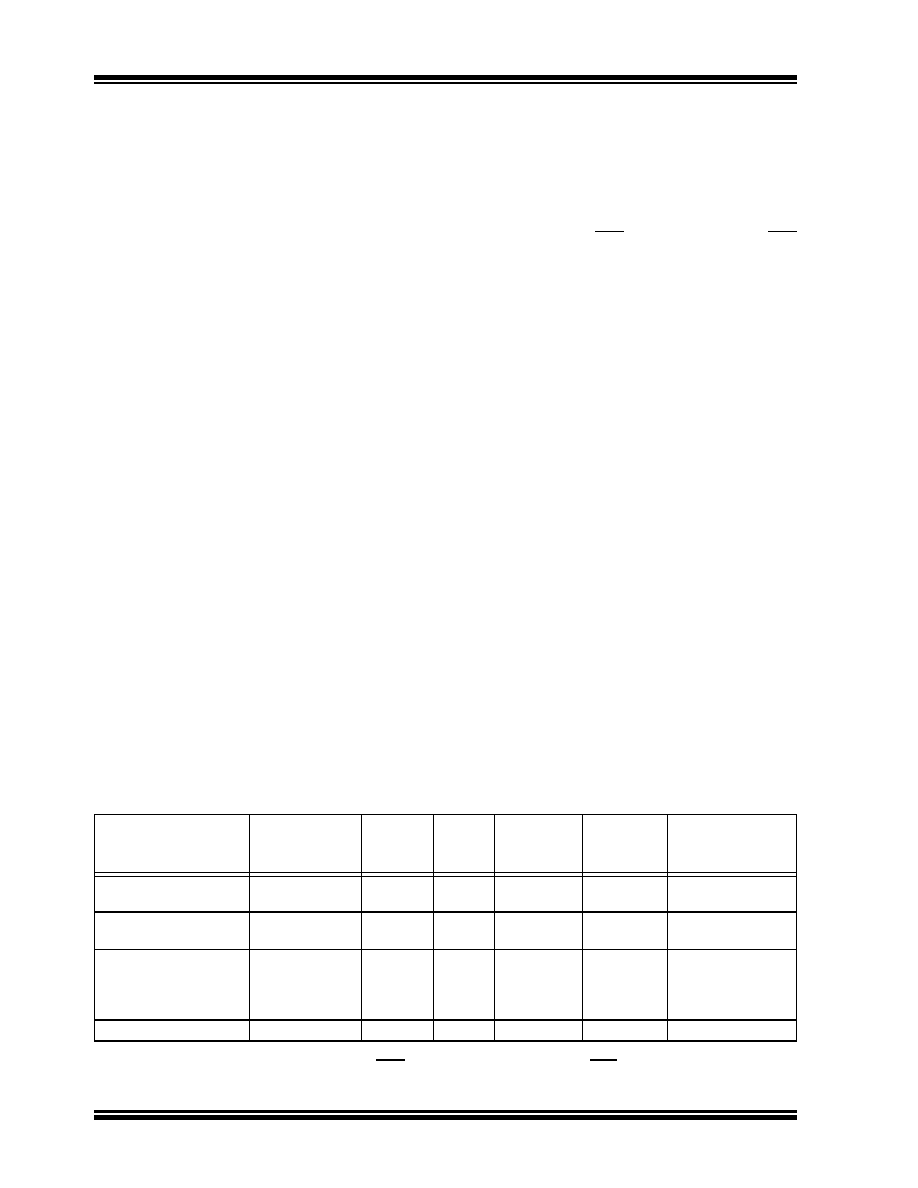

TABLE 4-1:

DATA RATE, OUTPUT NOISE AND DIGITAL FILTER SPECIFICATIONS BY DEVICE

Device

Output Data

Rate (tCONV)

Output

Noise

(VRMS)

Primary

Notch

(Hz)

Sample

Frequency

(fS)

Internal

Clock

fOSC

50/60 Hz Rejection

MCP3550-50

80.00 ms

2.5

50

25600 Hz

102.4 kHz

-120 dB min. at

50 Hz

MCP3550-60

66.67 ms

2.5

60

30720 Hz

122.88 kHz

-120 dB min. at

60 Hz

MCP3551

72.73 ms

2.5

55

28160 Hz

112.64 kHz

-82 dB min. from

48 Hz to 63 Hz. -

82 dB at 50 Hz and

-88 dB at 60 Hz

MCP3553

16.67 ms

6

240

30720 Hz

122.88 kHz

Not Applicable

Note:

For the first conversion after exiting Shutdown, tCONV must include an additional 144 fOSC periods before

the conversion is complete and the RDY (Ready) flag appears on SDO/RDY.

相关PDF资料 |

PDF描述 |

|---|---|

| LGU2D271MELY | CAP ALUM 270UF 200V 20% SNAP |

| MCP3551DM-PCTL | BOARD DEMO FOR MCP3551 |

| 0210490181 | CABLE JUMPER 1.25MM .203M 12POS |

| HL02150GTTR | INDUCTOR 15NH 200MA 0402 |

| SCRH6D28-180 | INDUCTOR SMD 18UH 1.32A 10KHZ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCP355XDV-MS1 | 功能描述:数据转换 IC 开发工具 MCP355X Sensor App Dev Brd RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| MCP3901 | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Two Channel Analog Front End |

| MCP3901_10 | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Two-Channel Analog Front End |

| MCP3901_11 | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Two-Channel Analog Front End Portable Instrumentation |

| MCP3901_12 | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Energy Meter Reference Design |

发布紧急采购,3分钟左右您将得到回复。