- 您现在的位置:买卖IC网 > PDF目录45328 > MK1492-04RTR 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 PDF资料下载

参数资料

| 型号: | MK1492-04RTR |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| 封装: | 0.150 INCH, SSOP-28 |

| 文件页数: | 4/8页 |

| 文件大小: | 102K |

| 代理商: | MK1492-04RTR |

MK1492-04

OPTi Firestar+ Clock Source

MDS1492-04C

4

Revision 4308

Printed 4/30/98

MicroClock Division of ICS1271 Parkmoor Ave.San JoseCA95126(408)295-9800tel(408)295-9818fax

PRELIMINARY INFORMATION

ICRO

CLOCK

Special Considerations When Using the HOST Clocks

The MK1492-04 has some pins that combine multiple outputs on a single pin. It also has a unique mode of

operation when used with 2.5 V microprocessors. This mode enables higher-strength output drivers in order

to maintain the timing specifications.

EHOST1, HOST2

The amplitude and drive strength of EHOST1 and HOST2 are controlled by VDDHOST1,2. When

VDDHOST1,2 is at 2.5 V (recognized at power up), the MK1492-04 automatically strengthens those

output drivers. No other changes are required by the user. EHOST1 should be connected to Firestar+ and

HOST2 connected to the CPU.

HOST3, HOST4

The amplitude of HOST3 and HOST4 is controlled by VDDHOST3,4. However, the drive strength for

HOST3 and HOST4 is not automatically strengthened when VDDHOST3,4 is set to 2.5 V. The output

drive on HOST3 and HOST4 at 2.5 V will be about 50% of that available at 3.3 V.

HOST5-HOST8

HOST5, HOST6, HOST7, and HOST8 combine four output drivers on two pins. HOST5 and HOST6

are always enabled, but HOST7 and HOST8 are controlled by the DS input (pin 19). As explained on

page 8, the DS input is sampled at VDD power up and at exit from the “Power Down” state. When the

latch is at logic 1, output drivers for HOST7 and HOST8 are tristated. When the latch is at logic 0, the

output drivers for HOST7 andHOST8 are enabled, thus providing the equivalent of two output clocks on

each pin (18 and 19). This is useful for supporting two SODIMM sockets and automatically sensing at

system power up if the second SODIMM is inserted. As one example, HOST5 and HOST6 are connected

to the two clock pins of the first SODIMM; HOST7 andHOST8 are connected to the second SODIMM;

DS is tied to the ground pin of the second socket with a series 10 k

resistor. If the second SODIMM is

present, it will pull the DS pin low and enable HOST7 and HOST8.

Note that HOST5, 6, 7, and 8 are supplied by the main MK1492-04 VDD supply, so only 3.3 V outputs are

supported on these pins.

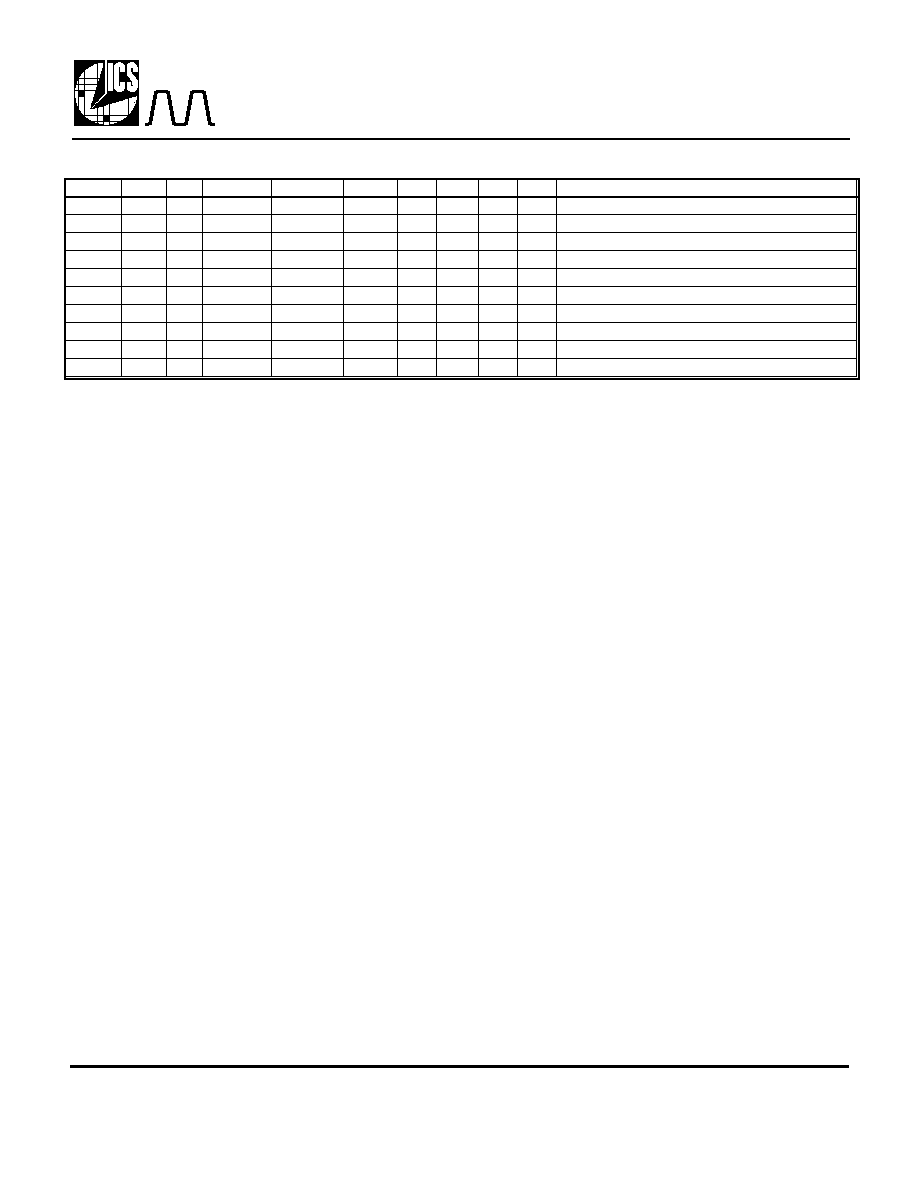

Power Down Control Table

PCISTP# CPUS# CSSS

MODE

HOST1:4,7,8 HOST5,6 PCI

PCIF 48/24 14.3 DESCRIPTION

X

0

X

Power Down

LOW

LOW LOW LOW LOW All outputs low. PLLs and Oscillator off.

0

M

0

CPU SLOW

33MHz

33 MHz LOW 16.6M ON

ON Host smooth transition to/from 33 MHz. PCI low.

M

0

PLL STOP

LOW

LOW LOW LOW

ON Oscillator on. PLLs off.

1

M

0

CPU SLOW

33MHz

33 MHz 16.6M 16.6M ON

ON Host smooth transition to/from 33 MHz.

0

1

X

PCI STOP

ON

LOW

ON

ON PCI clocks synchronously enter and leave low state.

M

1

X

ON

ON All Clocks On.

1

X

ON

ON All Clocks On.

0

M

1

ON

LOW

ON

ON Host & PCI synchronously enter and leave low state.

M

1

PLL STOP

LOW

LOW LOW LOW

ON Oscillator on. PLLs off.

1

M

1

CPU STOP

ON

LOW

ON

ON Host synchronously enter and leave low state.

Key: 1 = connected to VDD, 0 = connected to ground, M = 1.4 V ±0.2 V, X = any valid logic level, Combination Input/Outputs should be

connected to VDD or Ground through a 10 k

resistor as shown on page 8.

相关PDF资料 |

PDF描述 |

|---|---|

| MK1492-04R | 75 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO28 |

| MK1493-01G | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| MK1493-01G | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| MK1493-01GLF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| MK1493-01GTR | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK1493-01 | 制造商:ICS 制造商全称:ICS 功能描述:PCI Clock Generator |

| MK1493-01G | 制造商:ICS 制造商全称:ICS 功能描述:PCI Clock Generator |

| MK1493-01GTR | 制造商:ICS 制造商全称:ICS 功能描述:PCI Clock Generator |

| MK1493-03B | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:PCI CLOCK GENERATOR |

| MK1493-03BGILF | 制造商:Integrated Device Technology Inc 功能描述:DIFFERENTIAL SPREAD SPECTRUM CLOCK DRIVER, TSSOP16 - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。