- 您现在的位置:买卖IC网 > PDF目录8989 > MK1574-01SILF (IDT, Integrated Device Technology Inc)IC PLL FRAME RATE COMM 16-SOIC PDF资料下载

参数资料

| 型号: | MK1574-01SILF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 6/10页 |

| 文件大小: | 0K |

| 描述: | IC PLL FRAME RATE COMM 16-SOIC |

| 标准包装: | 48 |

| 类型: | 时钟/频率合成器 |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:3 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 8kHz |

| 除法器/乘法器: | 无/是 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 管件 |

MK1574

3.3 VOLT FRAME RATE COMMUNICATIONS PLL

CLOCK SYNTHESIZER

IDT / ICS 3.3 VOLT FRAME RATE COMMUNICATIONS PLL

5

MK1574

REV F 111605

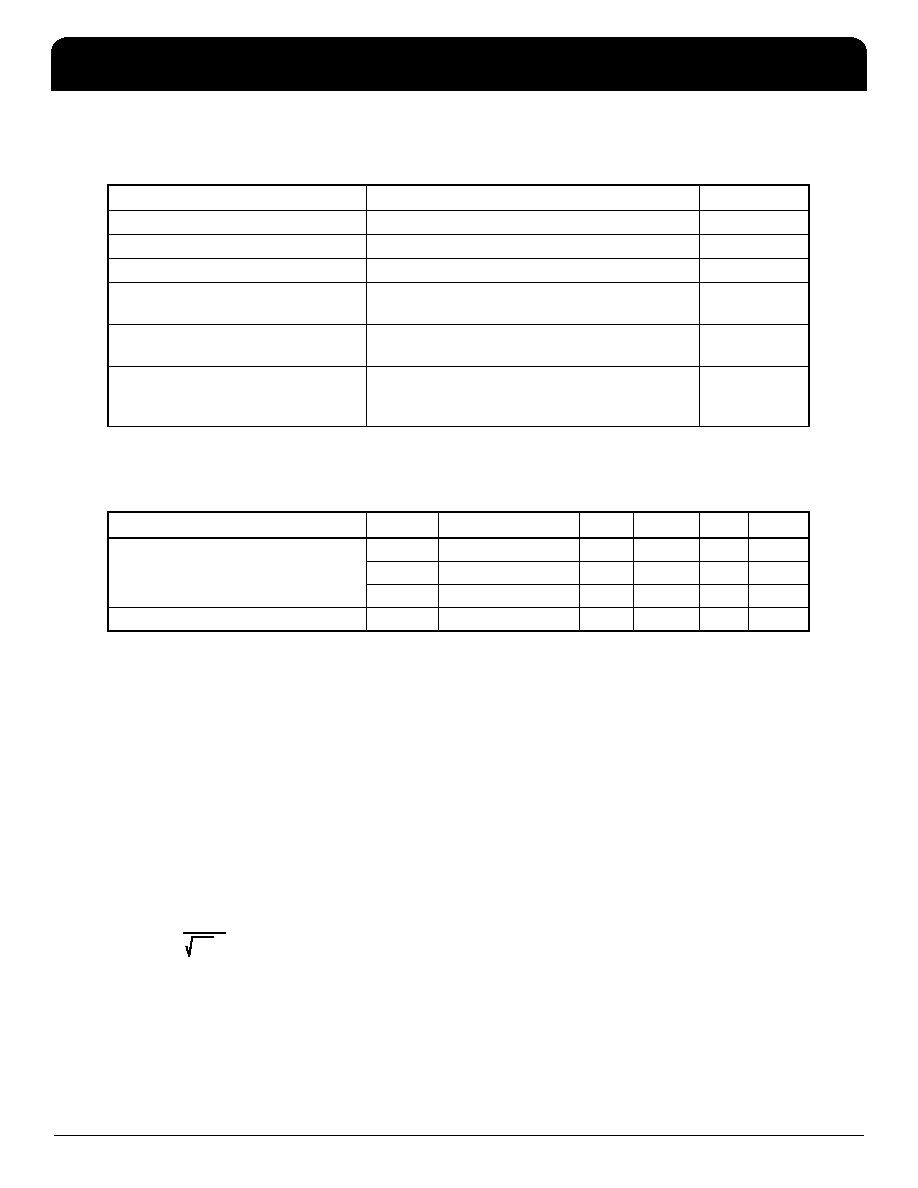

AC Electrical Characteristics

VDD = 3.3 V, Ambient Temperature 0 to +70

°C, unless stated otherwise

Note 1: All multipliers as shown in the table on page two are exact, and are stored in ROM on the chip.

Thermal Characteristics

Loop Bandwidth and Loop Filter Component Selection

The series-connected capacitor and resistor between CAP1 and CAP2 (pins 4 and 6) determine the dynamic

characteristics of the phase-locked loop. The capacitor must have very low leakage, therefore a high quality

ceramic capacitor is recommended. DO NOT use any type of polarized or electrolytic capacitor. The series

connected capacitor and resistor between CAP1 and CAP2 (pins 4 and 6) determine the dynamic characteristics of

the phase-locked loop. The capacitor must have very low leakage, therefore a high quality ceramic capacitor is

recommended. DO NOT use any type of polarized or electrolytic capacitor. Ceramic capacitors should have C0G or

NP0 dielectric. Avoid high-K dielectrics like Z5U and X7R; these and other ceramics which have piezoelectric

properties allow mechanical vibration in the system to increase the output jitter because the mechanical energy is

converted directly to voltage noise on the VCO input.

The values of the RC network determine the bandwidth of the PLL. The values of the loop filter components are

calculated using the constants K1 and K2 from the Loop Filter Constants table (page 7). The loop bandwidth is set

by the capacitor C and the constant K1 using the formula:

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

Input Frequency

fIN

8.000

kHz

Output Clock Rise Time

tOR

0.8 to 2.0 V

1.5

ns

Output Clock Fall Time

tOF

2.0 to 0.8 V

1.5

ns

Output Clock Duty Cycle,

High time

tDC

At VDD/2

40

49 to 51

60

%

Absolute Clock Period

Jitter

1ns

Actual Mean Frequency

Error Versus Target (note

1)

Any clock selection

0

ppm

Parameter

Symbol

Conditions

Min.

Typ.

Max.

Units

Thermal Resistance Junction to

Ambient

θ

JA

Still air

120

°C/W

θ

JA

1 m/s air flow

115

°C/W

θ

JA

3 m/s air flow

105

°C/W

Thermal Resistance Junction to Case

θ

JC

58

°C/W

BW (Hz) =

C

K1

Equation 1

相关PDF资料 |

PDF描述 |

|---|---|

| MS27474E16F6S | CONN RCPT 6POS JAM NUT W/SCKT |

| VI-J41-MZ-F4 | CONVERTER MOD DC/DC 12V 25W |

| VI-BN0-MV-F3 | CONVERTER MOD DC/DC 5V 150W |

| VI-2TX-MY-F1 | CONVERTER MOD DC/DC 5.2V 50W |

| LTC8043FN8#PBF | IC D/A CONV 12BIT SERIAL 8-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK1574-01SILFTR | 功能描述:时钟发生器及支持产品 3.3V FRAME RATE COMMUNICATION PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK1574-01SITR | 功能描述:IC PLL FRAME RATE COMM 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MK1574-01SLF | 功能描述:时钟发生器及支持产品 3.3V FRAME RATE COMMUNICATION PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK1574-01SLFTR | 功能描述:时钟合成器/抖动清除器 3.3V FRAME RATE COMMUNICATION PLL RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| MK1574-01STR | 功能描述:IC PLL FRAME RATE COMM 16-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。