- 您现在的位置:买卖IC网 > PDF目录2098 > MK1574-01STR (IDT, Integrated Device Technology Inc)IC PLL FRAME RATE COMM 16-SOIC PDF资料下载

参数资料

| 型号: | MK1574-01STR |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 4/10页 |

| 文件大小: | 0K |

| 描述: | IC PLL FRAME RATE COMM 16-SOIC |

| 产品变化通告: | Product Discontinuation 13/May/2009 |

| 标准包装: | 2,500 |

| 类型: | 时钟/频率合成器 |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:3 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 8kHz |

| 除法器/乘法器: | 无/是 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 带卷 (TR) |

MK1574

3.3 VOLT FRAME RATE COMMUNICATIONS PLL

CLOCK SYNTHESIZER

IDT / ICS 3.3 VOLT FRAME RATE COMMUNICATIONS PLL

3

MK1574

REV F 111605

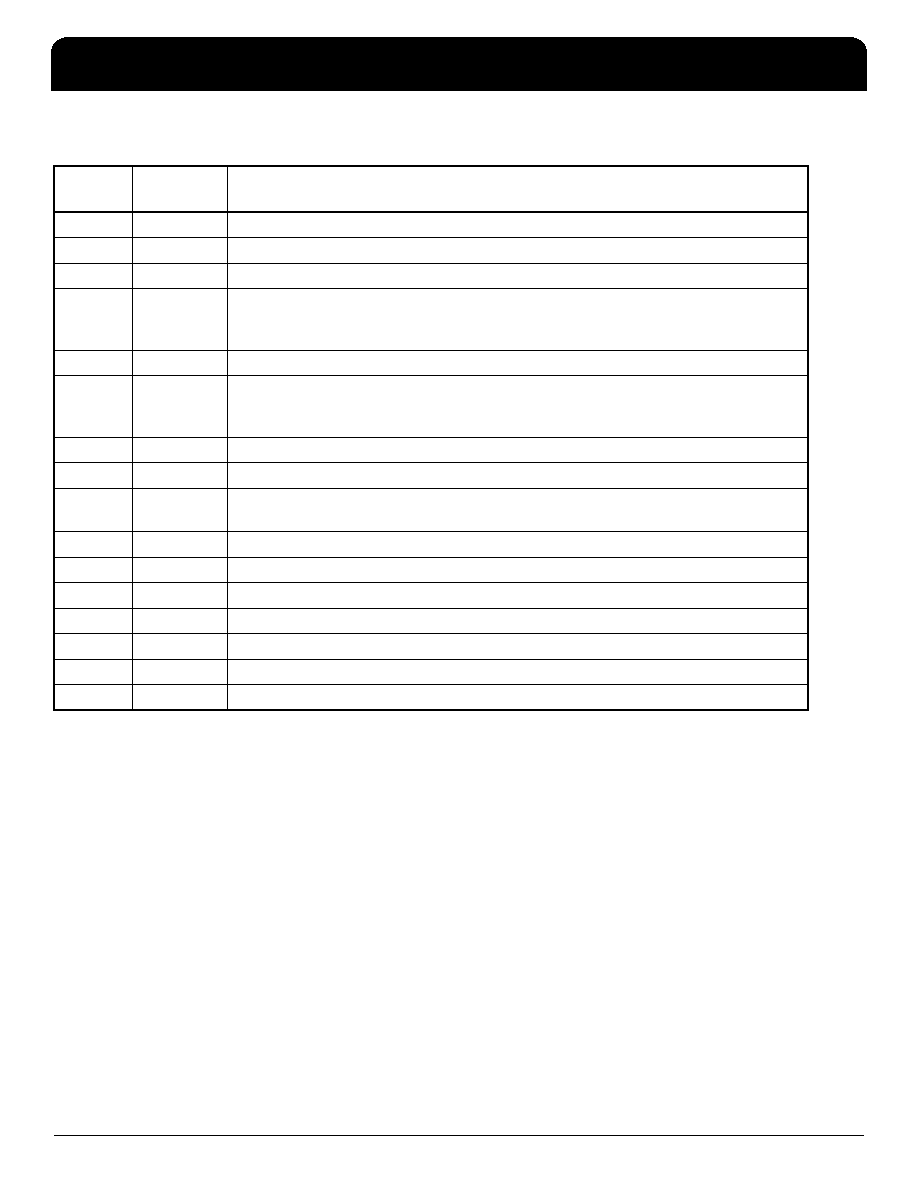

Pin Descriptions

External Components

The MK1574 requires a minimum number of external components for proper operation. An RC network (see the

section “Loop Bandwidth and Loop Filter Component Selection”) should be connected between CAP1 and CAP2 as

close tot he device as possible. Decoupling capacitors of 0.01F should be connected between VDD and GND on

pins 2, 3, 5 and 7, as close to the device as possible. A series termination resistor of 33

may be used close to

each clock output pin to reduce reflections.

Pin

Number

Pin

Name

Pin

Type

Pin Description

1

ICLK

Input

Clock input. Connect to an 8 kHz clock input.

2

VDD

Power

Connect to 3.3 V.

3

VDD

Power

Connect to 3.3 V.

4

CAP1

Input

Connect to a ceramic capacitor and a resistor in series between this pin and

CAP2. Refer to the section “Loop Bandwidth and Loop Filter Component

Selection”.

5

GND

Power

Connect to ground.

6

CAP2

Power

Connect to a ceramic capacitor and a resistor in series between this pin and

CAP1. Refer to the section “Loop Bandwidth and Loop Filter Component

Selection”.

7

GND

Power

Connect to ground.

8

FS0

Input

Frequency select 0. Determines CLK outputs per table above.

9

8KOUT

Output

Recovered 8 kHz output clock. Can be low jitter, better duty cycle than clock

input.

10

CLK1

Output

Clock 1 determined by status of FS3:0 per table above.

11

CLK2

Output

Clock 2 determined by status of FS3:0 per table above.

12

CLK3

Output

Clock 3 determined by status of FS3:0 per table above.

13

FS1

Input

Frequency select 1. Determines CLK outputs per table above.

14

FS2

Input

Frequency select 2. Determines CLK outputs per table above.

15

NC

—

No connect. Do not connect anything to this pin.

16

FS3

Input

Frequency select 3. Determines CLK outputs per table above.

相关PDF资料 |

PDF描述 |

|---|---|

| MK1581-01GILF | IC CLK GENERATOR T1/E1 16-TSSOP |

| MK1709AGLF | IC CLK GENERATOR LOW EMI 8-TSSOP |

| MK1714-02RLF | IC CLK MULT SPRD SPECTRUM 20QSOP |

| MK1726-08SLF | IC CLK GEN SPREAD SPECTRUM 8SOIC |

| MK2049-45SITR | IC CLK PLL COMM 3.3V 20-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK1575-01G | 功能描述:IC CLK RECOVERY PLL 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| MK1575-01GI | 功能描述:IC CLK RECOVERY PLL 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| MK1575-01GILF | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK1575-01GILFTR | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK1575-01GITR | 功能描述:IC CLK RECOVERY PLL 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。