- 您现在的位置:买卖IC网 > PDF目录132982 > MK2069-02GILF 160 MHz, OTHER CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | MK2069-02GILF |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, TSSOP-56 |

| 文件页数: | 1/20页 |

| 文件大小: | 347K |

| 代理商: | MK2069-02GILF |

MK2069-02

MDS 2069-02 G

1

Revision 050203

Integrated Circuit Systems, Inc. l 525 Race Street, San Jose, CA 95126 l tel (408) 295-9800 l

VCXO-Based Clock Jitter Attenuator and Translator

Description

The MK2069-02 is a VCXO (Voltage Controlled Crystal

Oscillator) based clock generator that offers system

synchronization, jitter attenuation and frequency

translation. It can accept an input clock over a wide

range of frequencies and produces a de-jittered, low

phase noise clock output. The device is optimized for

user configuration by providing access to all major PLL

divider functions. No power-up programming is needed

as configuration is pin selected. External VCXO loop

filter components provide an additional level of

performance tailoring.

The MK2069-02 features an adjustable phase detector

frequency, independent of the PLL frequency

multiplication factor, providing digital control over jitter

attenuation characteristics. This is accomplished by

two internal, programmable parallel dividers just prior

to the phase detector. One divider is applied to the

reference input clock, the other is applied to the PLL

feedback clock. Adjustment of the phase detector

frequency influences PLL loop bandwidth, damping

factor, input clock jitter frequency aliasing and input

jitter tolerance.

Features

Phase detector frequency is selectable over a wide

range with integer resolution. This allows control over

various PLL parameters such as loop bandwidth and

jitter attenuation characteristics.

Input clock frequency of <2kHz to 27MHz

Output clock frequency of 500kHz to 160MHz

PLL lock status output

VCXO-based clock generation offers very low jitter

and phase noise generation, even with low frequency

or jittery input clock.

PLL Clear function (CLR input) allows the VCXO to

free-run, offering a short term holdover function.

2nd PLL provides frequency translation of VCXO

PLL to higher or alternate output frequencies.

Device will free-run in the absence of an input clock

(or stopped input clock) based on the VCXO

frequency pulled to minimum frequency limit.

Low power CMOS technology

56 pin TSSOP package

Single 3.3V power supply

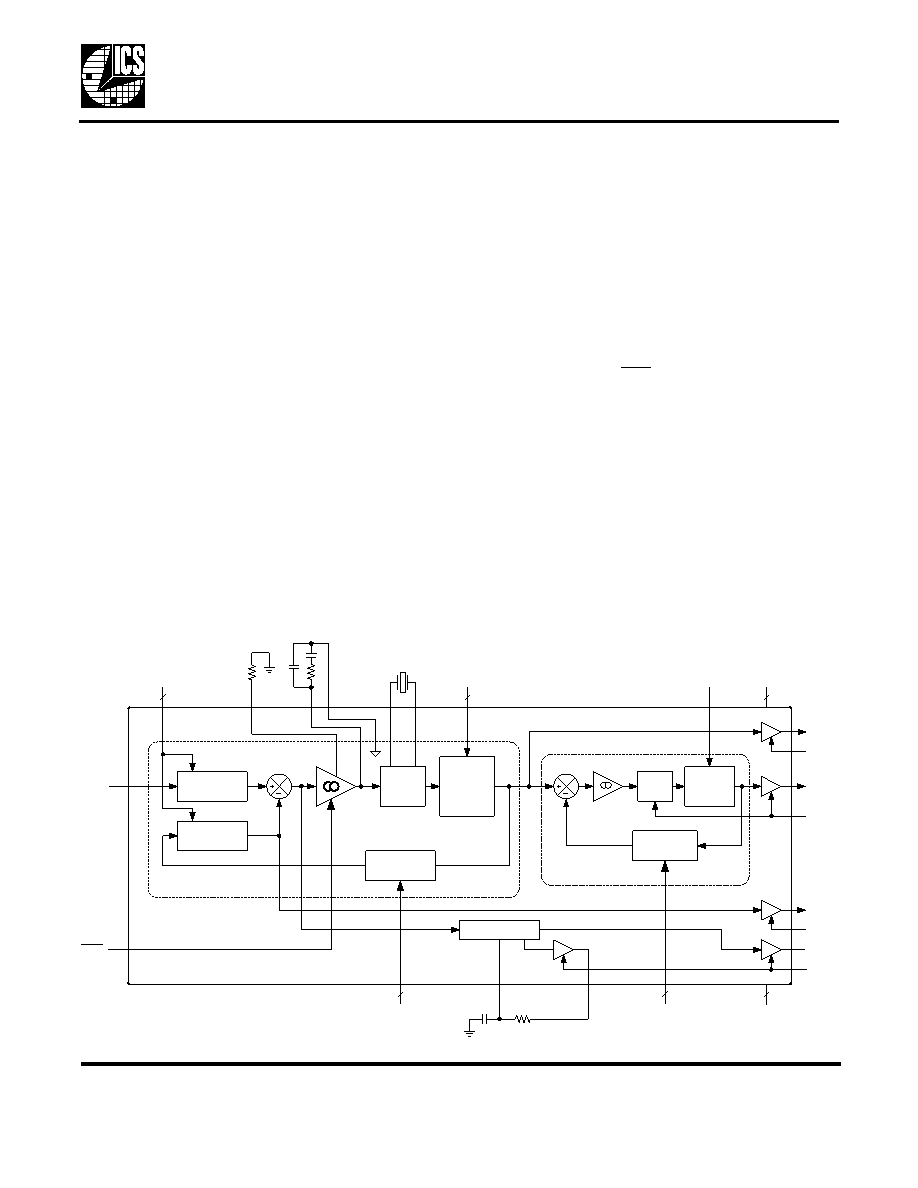

Block Diagram

C h arge

Pum p

VC XO

P u lla b le

xta l

VCL K

X2

X1

ISET

4

VDD

4

LF

FV D iv ide r

1 -40 96

PV D iv id e r

2 to 40 97

SV

Div id e r

1 ,2,4,6 ,8,

10 ,1 2 ,16

PV 1 1 :0

Pha se

Dete cto r

VC X O

PL L

FT D iv ide r

1-8

VC O

T ra n slato r

PL L

SV 2 :0

3

FV 11:0

FT 2 :0

3

TC L K

OE V

OE T

IC L K

LD

OE L

GN D

RC L K

OE R

L o ck D e te cto r

12

LD C

LD R

PV D iv id e r

2 to 40 97

12

CL R

ST

Div id e r

2, 1 6

ST

LF R

相关PDF资料 |

PDF描述 |

|---|---|

| MC9S08RD8P | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP28 |

| MC68HC05C4CFN | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PQCC44 |

| MC68HC05C4CP | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PDIP40 |

| MC68HC05C4MFN | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PQCC44 |

| MC68HSC05C4CL | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, CDIP40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK2069-03 | 制造商:ICS 制造商全称:ICS 功能描述:VCXO-Based Clock Translator with High Multiplication |

| MK2069-03GI | 功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| MK2069-03GITR | 功能描述:时钟发生器及支持产品 VCXO-BASED CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK2069-04 | 制造商:ICS 制造商全称:ICS 功能描述:VCXO-Based Universal Clock Translator |

| MK2069-04GI | 功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。