- 您现在的位置:买卖IC网 > PDF目录53728 > MK2745-24STRLF 60 MHz, VIDEO CLOCK GENERATOR, PDSO16 PDF资料下载

参数资料

| 型号: | MK2745-24STRLF |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 60 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| 封装: | 0.150 INCH, SOIC-16 |

| 文件页数: | 3/4页 |

| 文件大小: | 63K |

| 代理商: | MK2745-24STRLF |

MK2745-24

DVD/MPEG Clock Source

MDS 2745-24 B

3

Revision 100898

Printed 11/16/00

MicroClock Division of ICS1271 Parkmoor Ave.San JoseCA95126(408)295-9800tel(408)295-9818fax

I C R O

C LOC K

Parameter

Conditions

Minimum

Typical

Maximum

Units

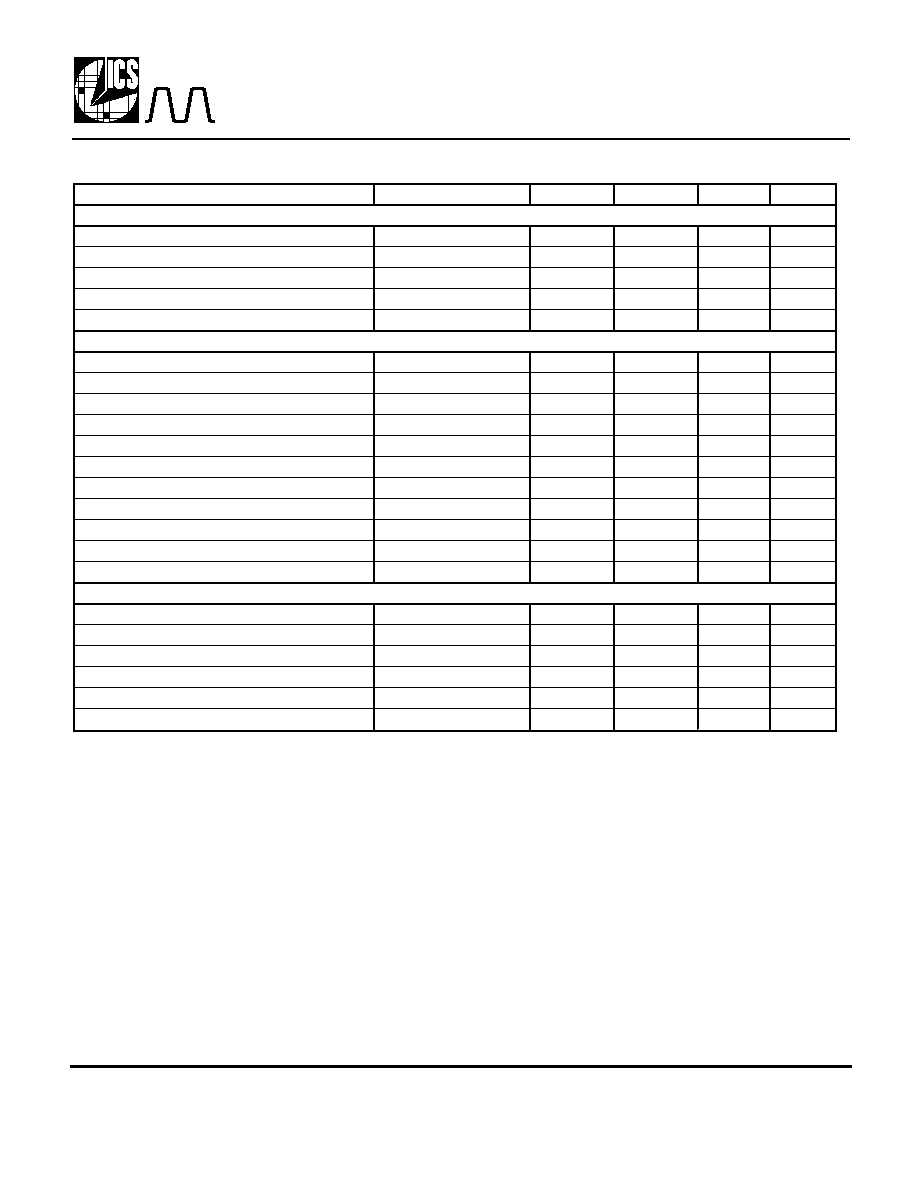

ABSOLUTE MAXIMUM RATINGS (note 1)

Supply voltage, VDD

Referenced to GND

7

V

Inputs and Clock Outputs

Referenced to GND

-0.5

VDD+0.5

V

Ambient Operating Temperature

0

70

°C

Soldering Temperature

Max of 20 seconds

260

°C

Storage temperature

-65

150

°C

DC CHARACTERISTICS (VDD = 5.0V unless noted)

Operating Voltage, VDD

3

5.5

V

Input High Voltage, VIH, X1/ICLK pin only

VDD/2 + 1

VDD/2

V

Input Low Voltage, VIL, X1/ICLK pin only

VDD/2

VDD/2 - 1

V

Input High Voltage, VIH

2

V

Input Low Voltage, VIL

0.8

V

Output High Voltage, VOH

IOH=-25mA

2.4

V

Output Low Voltage, VOL

IOL=25mA

0.4

V

Output High Voltage, VOH, CMOS level

IOH=-8mA

VDD-0.4

V

Operating Supply Current, IDD

No Load, note 2

37

mA

Short Circuit Current

Each output

±100

mA

Input Capacitance

7

pF

AC CHARACTERISTICS (VDD = 5.0V unless noted)

Input Frequency

27.000

MHz

Output Clock Rise Time

0.8 to 2.0V

1.5

ns

Output Clock Fall Time

2.0 to 0.8V

1.5

ns

Output Clock Duty Cycle

At VDD/2

40

60

%

Frequency synthesis error, all clocks

0

1

ppm

Absolute Jitter, short term

Variation from mean

200

ps

Electrical Specifications

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings could cause permanent damage to the device. Prolonged

exposure to levels above the operating limits but below the Absolute Maximums may affect device reliability.

2. With VDD=3.3V, processor clock at 60MHz, and ACLK at 12.288MHz.

External Components

The MK2745-24 requires a minimum number of external components for proper operation. Decoupling

capacitors of 0.1F should be connected between VDD and GND (on pins 4 and 5, and pins 13 and 12),

as close to the MK2745-24 as possible. A series termination resistor of 33

may be used for each clock

output. If a clock input is not used, the 27.00 MHz crystal must be connected as close to the chip as

possible. The crystal should be a fundamental mode (do not use third overtone), parallel resonant, 50ppm

or better. Crystal capacitors should be connected from pins X1 to ground and X2 to ground. The value of

these capacitors is given by the following equation, where CL is the crystal load capacitance: Crystal caps

(pF) = (CL-6) x 2. So for a crystal with 16pF load capacitance, two 20pF caps should be used.

相关PDF资料 |

PDF描述 |

|---|---|

| MK2745-24SLF | 60 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| MK2745-24STRLF | 60 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| MK2745-24SLF | 60 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| MK2746GLFT | 133.33 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| MK2746GLF | 133.33 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK2746 | 制造商:ICS 制造商全称:ICS 功能描述:DVD/MPEG CLOCK SOURCE |

| MK2746-01G | 功能描述:IC CLK SOURCE USB-DVD 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MK2746-01GLF | 功能描述:IC CLK SOURCE USB-DVD 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MK2746-01GLFTR | 功能描述:IC CLK SOURCE USB-DVD 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| MK2746-01GTR | 功能描述:IC CLK SOURCE USB-DVD 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。