- 您现在的位置:买卖IC网 > PDF目录53728 > MK3230-02S (INTEGRATED DEVICE TECHNOLOGY INC) 80 MHz, OTHER CLOCK GENERATOR, PDSO16 PDF资料下载

参数资料

| 型号: | MK3230-02S |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 80 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| 封装: | 0.150 INCH, SOIC-16 |

| 文件页数: | 2/4页 |

| 文件大小: | 68K |

| 代理商: | MK3230-02S |

MK3230

Portable System Clock Synthesizer

MDS 3230 F

2

Revision 022798

Printed 11/16/00

Integrated Circuit Systems, Inc.525 Race StreetSan JoseCA95126(408)295-9800telwww.icst.com

I C R O

C LOC K

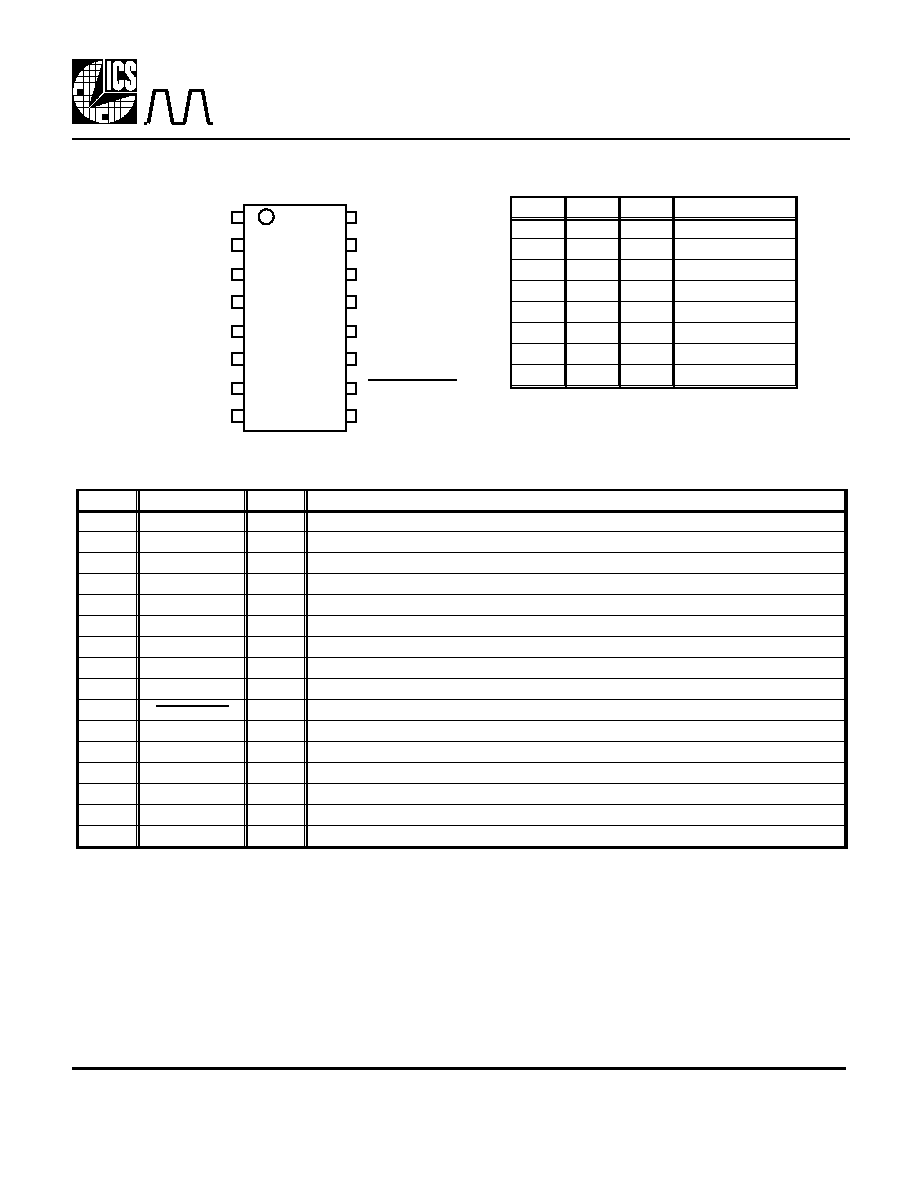

Pin Assignment

Number

Name

Type

Description

1

CPUS2

I

Select 2 for CPUCLK frequencies. See Table above.

2

X2

O

Crystal connection. Connect to 32.768 kHz crystal.

3

X1

I

Crystal connection. Connect to 32.768 kHz crystal.

4

VDD32

P

Separate power supply connection for 32.768kHz clock. Will operate to 2.0V.

5

VDD

P

Connect to +3.3V or +5V. Must be the same voltage as pin 13.

6

GND

P

Connect to ground.

7

24M

O

24 MHz floppy (or super I/O) clock output.

8

32K

O

32.768 kHz square wave clock output.

9

KBOUT

O

Keyboard clock output. Either 12MHz (-01) or 16MHz (-02)

10

PD24+KBD

I

Power Down 24M+keyboard. Shuts off both clock outputs (pins 7,9) when low.

11

14.3M

O

14.318 MHz system clock output. Do not drive a CRT PLL device with this output.

12

GND

P

Connect to ground.

13

VDD

P

Connect to +3.3V or +5V. Must be the same voltage as pin 5.

14

CPUCLK

O

CPUCLK output. See Table above.

15

CPUS0

I

Select 0 for CPUCLK frequencies. See Table above.

16

CPUS1

I

Select 1 for CPUCLK frequencies. See Table above.

Pin Descriptions

CPUS2 CPUS1 CPUS0 CPUCLK (MHz)

0

Off+14M off

0

1

80.00

0

1

0

25.00

0

1

66.66

1

0

20.00

1

0

1

50.00

1

0

33.33

1

4.00

CPU Clock Decoding

Type: I = Input, O = output, P = power supply connection

Power Down status: Output clocks will stop in a low state when powered down

1

8

9

16

2

3

4

5

6

7

10

11

12

13

14

15

CPUS1

PD24+KBD

KBOUT

CPUCLK

14.3M

CPUS0

VDD

GND

CPUS2

32K

X2

GND

24M

VDD32

VDD

X1

External Components

The MK3230 requires a minimum number of external components for proper operation. Decoupling

capacitors of 0.1F should be connected between VDD and GND, and VDD32 and GND, as close to the

MK3230 as possible. A 10k

series resistor should be used to filter the VDD32 pin. A series termination

resistor of 33

may be used for each clock output. The device does not require (nor do we recommend)

capacitors connected to the crystal pins. The 32.768 kHz crystal must be connected as close to the chip as

possible. See Application Brief MAB02 for a discussion on tuning for use on a real time clock (RTC).

Frequency transitions (except going to/from

off) will occur smoothly, and are compatible

with all 486 processors.

相关PDF资料 |

PDF描述 |

|---|---|

| MK3230-02SLFTR | 80 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| MK3230-02S | 80 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| MK3230-02SLF | 80 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| MK3711DMLFTR | 16 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| MK3711DMILFTR | 16 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK3230-02STR | 制造商:ICS 制造商全称:ICS 功能描述:Portable System Clock Synthesizer |

| MK3233 | 制造商:ICS 制造商全称:ICS 功能描述:Handheld System Clock Synthesizer |

| MK3233-01S | 制造商:ICS 制造商全称:ICS 功能描述:Handheld System Clock Synthesizer |

| MK3233-01STR | 制造商:ICS 制造商全称:ICS 功能描述:Handheld System Clock Synthesizer |

| MK3233-02S | 制造商:ICS 制造商全称:ICS 功能描述:Handheld System Clock Synthesizer |

发布紧急采购,3分钟左右您将得到回复。