- 您现在的位置:买卖IC网 > PDF目录382336 > MM54HCT109J (NATIONAL SEMICONDUCTOR CORP) Dual J-K Flip-Flops with Preset and Clear PDF资料下载

参数资料

| 型号: | MM54HCT109J |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 通用总线功能 |

| 英文描述: | Dual J-K Flip-Flops with Preset and Clear |

| 中文描述: | HCT SERIES, DUAL POSITIVE EDGE TRIGGERED J-KBAR FLIP-FLOP, COMPLEMENTARY OUTPUT, CDIP16 |

| 封装: | DIP-16 |

| 文件页数: | 3/4页 |

| 文件大小: | 123K |

| 代理商: | MM54HCT109J |

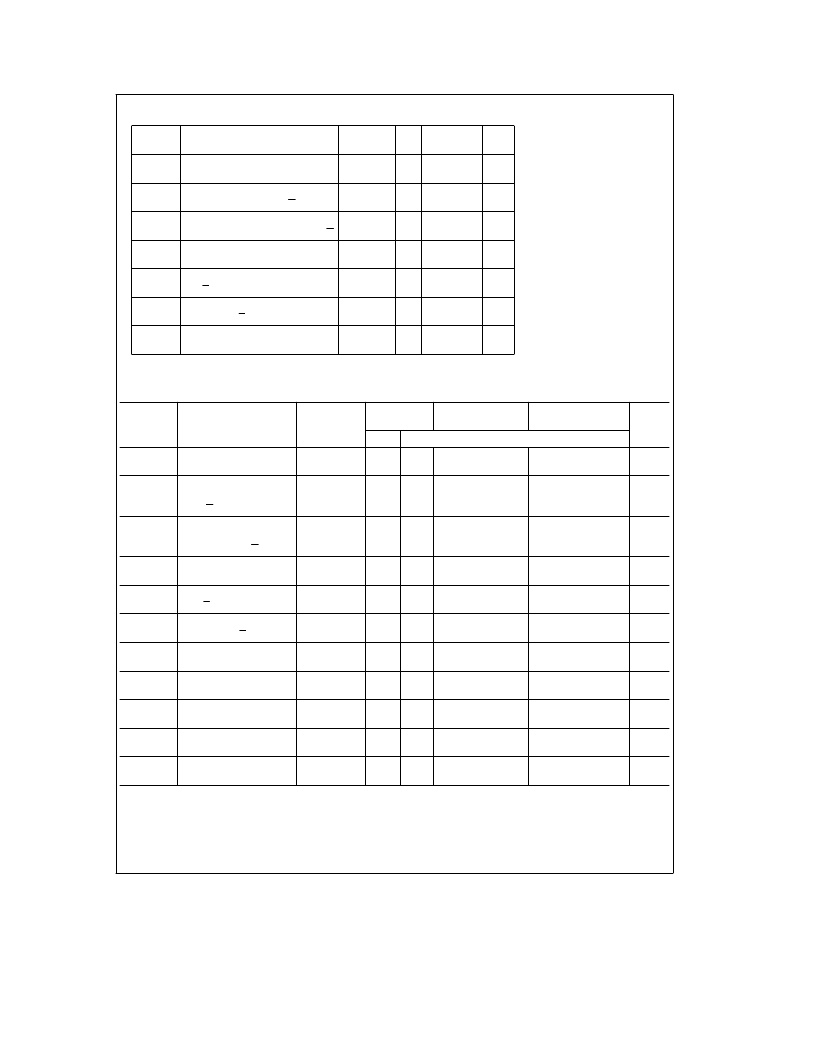

AC Electrical Characteristics

V

CC

e

5V, T

A

e

25

§

C, C

L

e

15 pF, t

r

e

t

f

e

6 ns

Symbol

Parameter

Conditions

Typ

Guaranteed

Limit

Units

f

MAX

Maximum Operating

Frequency

50

30

MHz

t

PHL

, t

PLH

Maximum Propagation

Delay from Clock to Q or Q

18

30

ns

t

PHL

, t

PLH

Maximum Propagation

Delay from Preset or Clear to Q or Q

18

30

ns

t

REM

Minimum Removal Time,

Preset or Clear to Clock

20

ns

t

S

Minimum Setup Time

J or K Clock

10

20

ns

t

H

Minimum Hold Time

Clock to J or K

b

3

0

ns

t

W

Minimum Pulse Width

Clock, Preset or Clear

8

16

ns

AC Electrical Characteristics

V

CC

e

5.0V

g

10%, C

L

e

50 pF, t

r

e

t

f

e

6 ns (unless otherwise specified)

T

A

e

25

§

C

74HCT

54HCT

Symbol

Parameter

Conditions

T

A

eb

40

§

to 85

§

C

T

A

eb

55

§

to 125

§

C

Units

Typ

Guaranteed Limits

f

MAX

Maximum Operating

Frequency

27

22

18

MHz

t

PHL

, t

PLH

Maximum Propagation

Delay from Clock to

Q or Q

22

35

44

52

ns

t

PHL

, t

PLH

Maximum Propagation

Delay from Preset

or Clear to Q or Q

22

35

44

52

ns

t

REM

Minimum Removal Time

Preset or Clear to Clock

20

25

30

ns

t

S

Minimum Setup Time

J or K to Clock

10

20

25

30

ns

t

H

Minimum Hold Time

Clock to J or K

b

3

0

0

0

ns

t

W

Minimum Pulse Width

Clock, Preset or Clear

16

20

24

ns

t

r

, t

f

Maximum Input Rise and

Fall Time

500

500

500

ns

t

THL

, t

TLH

Maximum Output

Rise and Fall Time

15

19

22

ns

C

PD

Power Dissipation

Capacitance (Note 5)

(per flip-flop)

35

pF

C

IN

Maximum Input

Capacitance

5

10

10

10

pF

Note 5:

C

PD

determines the no load dynamic power consumption, P

D

e

C

PD

V

CC2

f

a

I

CC

V

CC

, and the no load dynamic current consumption, I

S

e

C

PD

V

CC

f

a

I

CC

.

3

相关PDF资料 |

PDF描述 |

|---|---|

| MM74HCT109J | Dual J-K Flip-Flops with Preset and Clear |

| MM74HCT109N | Dual J-K Flip-Flops with Preset and Clear |

| MM74HCT112 | Dual J-K Flip-Flops with Preset and Clear |

| MM54HCT112 | Dual J-K Flip-Flops with Preset and Clear |

| MM54HCT76 | Dual J-K Flip-Flops with Preset and Clear |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MM54HCT112 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:Dual J-K Flip-Flops with Preset and Clear |

| MM54HCT138E/883 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3-To-8-Line Demultiplexer |

| MM54HCT138J | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3-To-8-Line Demultiplexer |

| MM54HCT138J/883 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3-To-8-Line Demultiplexer |

| MM54HCT138J/883C | 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。