- 您现在的位置:买卖IC网 > PDF目录382335 > MM74HC137J (NATIONAL SEMICONDUCTOR CORP) 3-to-8 Line Decoder With Address Latches (Inverted Output) PDF资料下载

参数资料

| 型号: | MM74HC137J |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 通用总线功能 |

| 英文描述: | 3-to-8 Line Decoder With Address Latches (Inverted Output) |

| 中文描述: | HC/UH SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, CDIP16 |

| 封装: | CERAMIC, DIP-16 |

| 文件页数: | 3/6页 |

| 文件大小: | 131K |

| 代理商: | MM74HC137J |

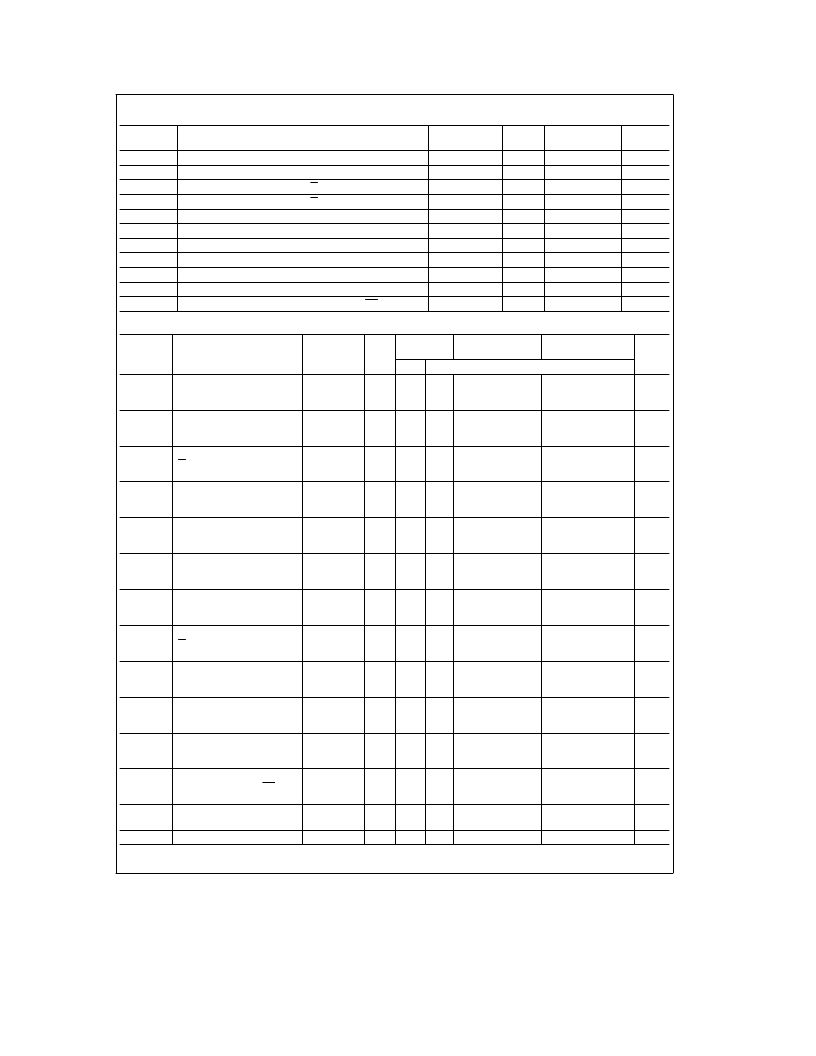

AC Electrical Characteristics

V

CC

e

5V, T

A

e

25

§

C, C

L

e

15 pF, t

r

e

t

f

e

6 ns

Symbol

Parameter

Conditions

Typ

Guaranteed

Limit

Units

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

PLH

t

PHL

t

S

t

H

t

W

AC Electrical Characteristics

C

L

e

50 pF, t

r

e

t

f

e

6 ns (unless otherwise specified)

Maximum Propagation Delay, A, B or C to any Y Output

14

29

ns

Maximum Propagation Delay, A, B or C to any Y Output

20

42

ns

Maximum Propagation Delay G2 to any Y Output

12

22

ns

Maximum Propagation Delay G2 to any Y Output

15

34

ns

Maximum Propagation Delay G1 to any Output

13

25

ns

Maximum Propagation Delay GL to any Output

17

34

ns

Maximum Propagation GL to Output

15

30

ns

Maximum Propagation Delay GL to Output

22

34

ns

Minimum Setup Time at A, B and C Inputs

20

ns

Minimum Hold Time at A, B and C Inputs

0

ns

Minimum Pulse Width of Enabling Pulse at GL

16

ns

T

A

e

25

§

C

74HC

54HC

Symbol

Parameter

Conditions

V

CC

T

A

eb

40 to 85

§

C

Guaranteed Limits

T

A

eb

55 to 125

§

C

Units

Typ

t

PLH

Maximum Propagation Delay

A, B or C to any Y Output

2.0V

4.5V

6.0V

85

17

14

170

34

29

214

43

36

253

51

43

ns

ns

ns

t

PHL

Maximum Propagation Delay

A, B or C to any Y Output

2.0V

4.5V

6.0V

120

24

20

240

48

41

302

60

51

358

72

61

ns

ns

ns

t

PLH

Maximum Propagation Delay

G2 to any Y Output

2.0V

4.5V

6.0V

65

13

11

130

26

22

164

33

28

194

39

33

ns

ns

ns

t

PLH

Maximum Propagation

Delay G1 to Output

2.0V

4.5V

6.0V

75

15

13

150

30

26

189

38

32

224

45

38

ns

ns

ns

t

PHL

Maximum Propagation

Delay G1 to Output

2.0V

4.5V

6.0V

98

20

17

195

39

33

246

49

42

291

58

49

ns

ns

ns

t

PLH

Maximum Propagation

Delay GL to Output

2.0V

4.5V

6.0V

88

18

15

175

35

30

221

44

37

261

52

44

ns

ns

ns

t

PHL

Maximum Propagation

Delay GL to Output

2.0V

4.5V

6.0V

125

25

21

250

50

43

315

63

54

373

75

63

ns

ns

ns

t

PHL

Maximum Propagation Delay

G2, to any Y Output

2.0V

4.5V

6.0V

98

20

17

195

39

33

246

49

42

291

58

49

ns

ns

ns

t

S

Minimum Setup Time

at A, B and C inputs

2.0V

4.5V

6.0V

100

20

17

125

25

21

150

30

25

ns

ns

ns

t

H

Minimum Hold Time

at A, B and C inputs

2.0V

4.5V

6.0V

50

10

8

63

13

11

75

15

13

ns

ns

ns

t

TLH

, t

THL

Output Rise and

Fall Time

2.0V

4.5V

6.0V

30

8

7

75

15

13

95

19

16

110

22

19

ns

ns

ns

t

W

Minimum Pulse Width

of Enabling Pulse at GL

2.0V

4.5V

6.0V

80

16

14

100

20

18

120

24

21

ns

ns

ns

C

PD

Power Dissipation

Capacitance (Note 5)

75

pF

C

IN

Note 5:

C

PD

determines the no load dynamic power consumption, P

D

e

C

PD

V

CC2

f

a

I

CC

V

CC

, and the no load dynamic current consumption, I

S

e

C

PD

V

CC

f

a

I

CC

.

Maximum Input Capacitance

5

10

10

10

pF

3

相关PDF资料 |

PDF描述 |

|---|---|

| MM74HC137N | 3-to-8 Line Decoder With Address Latches (Inverted Output) |

| MM54HC137 | 3-to-8 Line Decoder With Address Latches (Inverted Output) |

| MM54HC137J | 3-to-8 Line Decoder With Address Latches (Inverted Output) |

| MM74HC153 | Zener Diode 225 mW 5.1 V ±2%SOT-23; Package: SOT-23 (TO-236) 3 LEAD; No of Pins: 3; Container: Tape and Reel; Qty per Container: 3000 |

| MM74HC194 | 4-Bit Bidirectional Universal Shift Register |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MM74HC137N | 制造商:NSC 制造商全称:National Semiconductor 功能描述:3-to-8 Line Decoder With Address Latches (Inverted Output) |

| MM74HC138 | 制造商:FAIRCHILD 制造商全称:Fairchild Semiconductor 功能描述:3-to-8 Line Decoder |

| MM74HC138J | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3-To-8-Line Demultiplexer |

| MM74HC138J/A+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:3-To-8-Line Demultiplexer |

| MM74HC138M | 功能描述:编码器、解码器、复用器和解复用器 3-to-8 Line Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。