- 您现在的位置:买卖IC网 > PDF目录382333 > MM74HCT190 (National Semiconductor Corporation) Level changes on Enable or Down/Up can be made regardless of the level of the clock PDF资料下载

参数资料

| 型号: | MM74HCT190 |

| 厂商: | National Semiconductor Corporation |

| 英文描述: | Level changes on Enable or Down/Up can be made regardless of the level of the clock |

| 中文描述: | 水平变化启用或向下/向上,可无论在时钟的水平 |

| 文件页数: | 1/8页 |

| 文件大小: | 170K |

| 代理商: | MM74HCT190 |

TL/F/5744

M

M

January 1988

MM54HCT190/MM74HCT190 Synchronous Decade Up/

Down Counters with Mode Control. MM54HCT191/

MM74HCT191 Synchronous Binary Up/Down Counters

with Mode Control

General Description

These high speed synchronous counters utilize advanced

silicon-gate CMOS technology. They possess the high noise

immunity and low power consumption of CMOS technology,

along with the speeds of low power Schottky TTL. These

circuits are synchronous, reversible, up/down counters. The

MM54HCT191/MM74HCT191 are 4-bit binary counters and

the MM54HCT190/MM74HCT190 are BCD counters.

Synchronous operation is provided by having all flip-flops

clocked simultaneously so that the outputs change simulta-

neously when so instructed by the steering logic. This mode

of operation eliminates the output counting spikes normally

associated with asynchronous (ripple clock) counters.

The outputs of the four master-slave flip-flops are triggered

on a low-to-high level transition of the clock input, if the

enable input is low. A high at the enable input inhibits count-

ing. The direction of the count is determined by the level of

the down/up input. When low, the counter counts up and

when high, it counts down.

These counters are fully programmable; that is, the outputs

may be preset to either level by placing a low on the load

input and entering the desired data at the data inputs. The

output will change independent of the level of the clock in-

put. This feature allows the counters to be used as divide by

N dividers by simply modifying the count length with the

preset inputs.

Two outputs have been made available to perform the cas-

cading function; ripple clock and maximum/minimum count.

The latter output produces a high level output pulse with a

duration approximately equal to one complete cycle of the

clock when the counter overflows or underflows. The ripple

clock output produces a low level output pulse equal in

width to the low level portion of the clock input when an

overflow or underflow condition exists. The counters can be

easily cascaded by feeding the ripple clock output to the

enable input of the succeeding counter if parallel clocking is

used, or to the clock input if parallel enabling is used. The

maximum/minimum count output can be used to accom-

plish look-ahead for high speed operation.

MM54HCT/MM74HCT devices are intended to interface be-

tween TTL and NMOS components and standard CMOS

devices. These parts are also plug-in replacements for LS-

TTL devices can be used to reduce power consumption in

existing designs.

Features

Y

Level changes on Enable or Down/Up can be made

regardless of the level of the clock.

Y

Low quiescent supply current: 80

m

A maximum

(74HCT Series)

Y

Low input current: 1

m

A maximum

Y

TTL compatible inputs

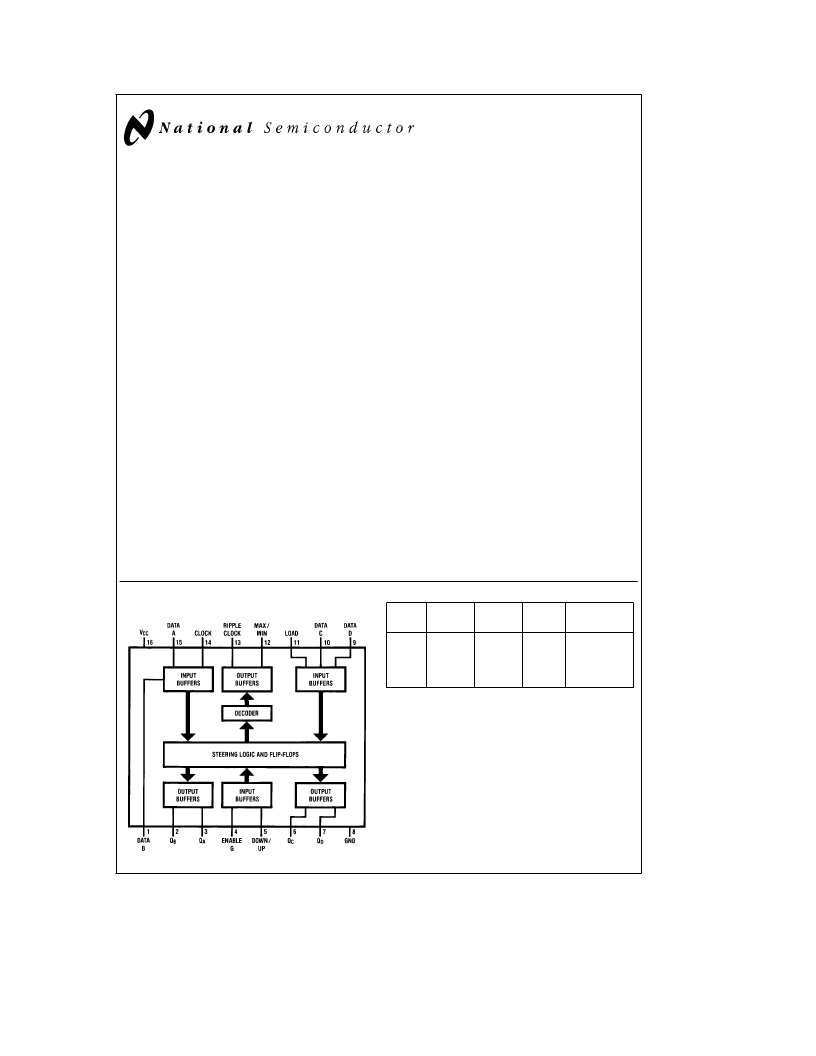

Connection Diagram

Dual-In-Line Package

TL/F/5744–1

Truth Table

Load

Enable

G

Down/

Up

Clock

Function

H

H

L

H

L

L

X

H

L

H

X

X

u

u

X

X

Count Up

Count Down

Load

No Change

Order Number MM54HCT190/191

or MM74HCT190/191

C

1995 National Semiconductor Corporation

RRD-B30M105/Printed in U. S. A.

相关PDF资料 |

PDF描述 |

|---|---|

| MM74HCT191 | Level changes on Enable or Down/Up can be made regardless of the level of the clock |

| MM54HCT193 | Lockwire |

| MM54HCT193J | SWITCH |

| MM74HCT193 | CLAMP |

| MM74HCT193J | CLAMP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MM74HCT191 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:Level changes on Enable or Down/Up can be made regardless of the level of the clock |

| MM74HCT193 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:Synchronous Binary Up/Down Counters |

| MM74HCT193J | 制造商:NSC 制造商全称:National Semiconductor 功能描述:Synchronous Binary Up/Down Counters |

| MM74HCT193N | 制造商:NSC 制造商全称:National Semiconductor 功能描述:Synchronous Binary Up/Down Counters |

| MM74HCT193WM | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。