- 您现在的位置:买卖IC网 > PDF目录45337 > MPC5200CVR466BR2 (FREESCALE SEMICONDUCTOR INC) 32-BIT, 400 MHz, MICROPROCESSOR, PBGA272 PDF资料下载

参数资料

| 型号: | MPC5200CVR466BR2 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA272 |

| 封装: | 27 X 27 MM, 1.27 MM PITCH, ROHS COMPLIANT, PLASTIC, BGA-272 |

| 文件页数: | 63/72页 |

| 文件大小: | 978K |

| 代理商: | MPC5200CVR466BR2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页当前第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

MPC5200B Data Sheet, Rev. 4

66

Freescale Semiconductor

3.3.2

Pull-up Requirements for the PCI Control Lines

If the PCI interface is NOT used (and internally disabled) the PCI control pins must be terminated as indicated by the PCI Local

Bus specification. This is also required for MOST/Graphics and Large Flash Mode.

PCI control signals always require pull-up resistors on the motherboard (not the expansion board) to ensure that they contain

stable values when no agent is actively driving the bus. This includes PCI_FRAME, PCI_TRDY, PCI_IRDY, PCI_DEVSEL,

PCI_STOP, PCI_SERR, PCI_PERR, and PCI_REQ.

3.3.3

Pull-up/Pull-down Requirements for MEM_MDQS Pins (SDRAM)

The MEM_MDQS[3:0] signals are not used with SDR memories and require pull-up or pull-down resistors in SDRAM mode.

3.3.4

.

Pull-up/Pull-down Requirements for MEM_MDQS Pins (DDR 16-bit

Mode)

The MEM_MDQS[1:0] signals are not used in DDR 16-bit mode and require pull-down resistors.

3.4

JTAG

The MPC5200B provides the user an IEEE 1149.1 JTAG interface to facilitate board/system testing. It also provides a Common

On-Chip Processor (COP) Interface, which shares the IEEE 1149.1 JTAG port. The COP Interface provides access to the

MPC5200B's embedded Freescale (formerly Motorola) MPC603e e300 processor. This interface provides a means for

executing test routines and for performing software development and debug functions.

3.4.1

JTAG_TRST

Boundary scan testing is enabled through the JTAG interface signals. The JTAG_TRST signal is optional in the IEEE 1149.1

specification but is provided on all processors that implement the PowerPC architecture. To obtain a reliable power-on reset

performance, the JTAG_TRST signal must be asserted during power-on reset.

3.4.1.1

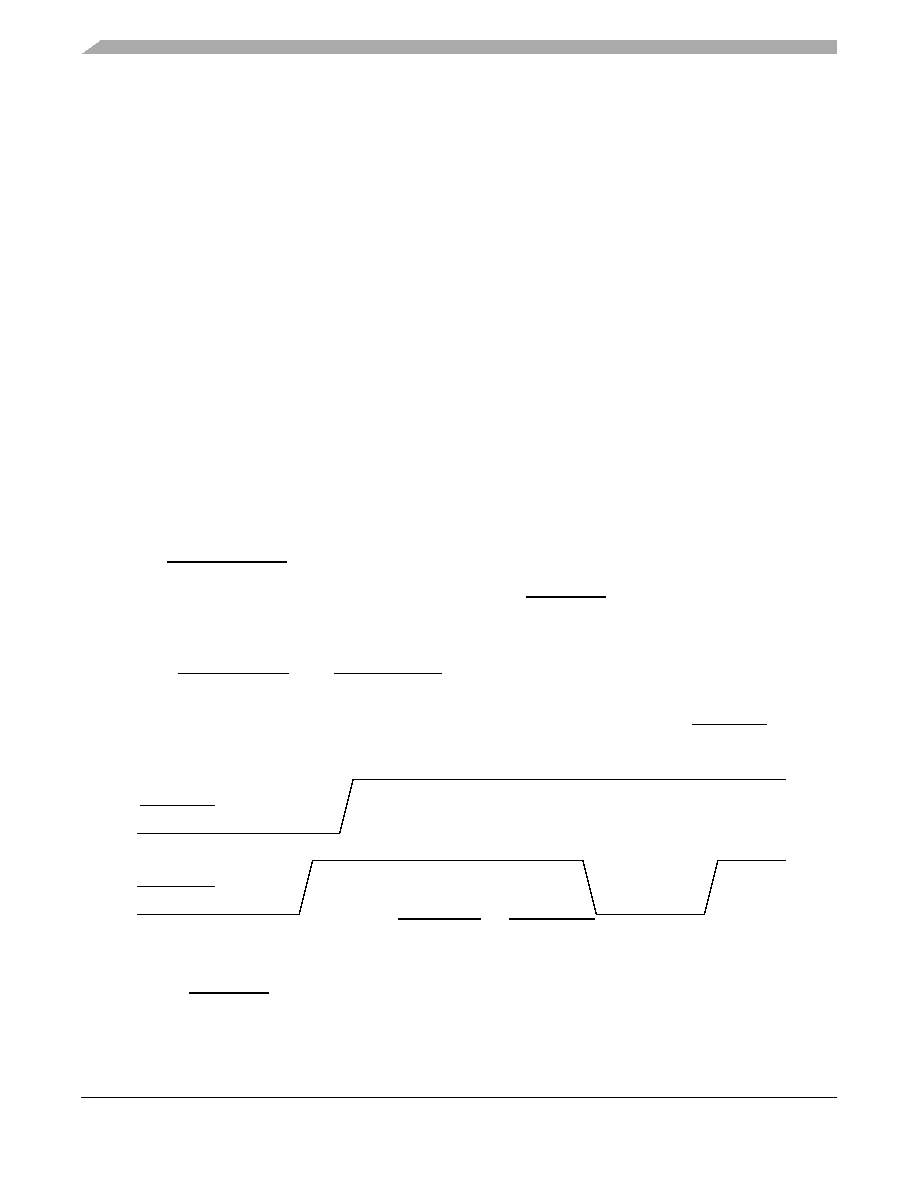

JTAG_TRST and PORRESET

The JTAG interface can control the direction of the MPC5200B I/O pads via the boundary scan chain. The JTAG module must

be reset before the MPC5200B comes out of power-on reset; do this by asserting JTAG_TRST before PORRESET is released.

For more details refer to the Reset and JTAG Timing Specification.

Figure 53. PORRESET vs. JTAG_TRST

3.4.1.2

Connecting JTAG_TRST

The wiring of the JTAG_TRST depends on the existence of a board-related debug interface. (see below)

JTAG_TRST

PORRESET

Required assertion of JTAG_TRST

Optional assertion of JTAG_TRST

相关PDF资料 |

PDF描述 |

|---|---|

| MPC5200VR400BR2 | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA272 |

| MPC5534MVF66 | MICROCONTROLLER, PBGA208 |

| MPC5534MZQ40 | MICROCONTROLLER, PBGA324 |

| MPC5534MZQ66 | MICROCONTROLLER, PBGA324 |

| MPC5534MZQ80 | FLASH, 80 MHz, MICROCONTROLLER, PBGA324 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC5200ID | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:MPC5200 Hardware Specifications |

| MPC5200VR400 | 功能描述:微处理器 - MPU NO-PB COMM 5200 400MHZ RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC5200VR400B | 功能描述:微处理器 - MPU HABANERO COMM PBFREE RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC5200VR400BR2 | 功能描述:IC MPU 32BIT 400MHZ 272-PBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:MPC52xx 标准包装:1 系列:AVR® ATmega 核心处理器:AVR 芯体尺寸:8-位 速度:16MHz 连通性:I²C,SPI,UART/USART 外围设备:欠压检测/复位,POR,PWM,WDT 输入/输出数:32 程序存储器容量:32KB(16K x 16) 程序存储器类型:闪存 EEPROM 大小:1K x 8 RAM 容量:2K x 8 电压 - 电源 (Vcc/Vdd):2.7 V ~ 5.5 V 数据转换器:A/D 8x10b 振荡器型:内部 工作温度:-40°C ~ 125°C 封装/外壳:44-TQFP 包装:剪切带 (CT) 其它名称:ATMEGA324P-B15AZCT |

| MPC52100J | 功能描述:厚膜电阻器 - 透孔 RoHS:否 制造商:Caddock 电阻:27 kOhms 容差:1 % 功率额定值:8 W 温度系数:50 PPM / C 系列:MS 端接类型:Axial 电压额定值:2 kV 工作温度范围:- 15 C to + 275 C 尺寸:8.89 mm Dia. x 23.11 mm L 封装:Bulk |

发布紧急采购,3分钟左右您将得到回复。