- 您现在的位置:买卖IC网 > PDF目录132964 > MPC7410THX450LE (MOTOROLA INC) 32-BIT, 450 MHz, RISC PROCESSOR, CBGA360 PDF资料下载

参数资料

| 型号: | MPC7410THX450LE |

| 厂商: | MOTOROLA INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 450 MHz, RISC PROCESSOR, CBGA360 |

| 封装: | 25 X 25 MM, 3.20 MM HEIGHT, 1.27 MM PITCH, CERAMIC, FCBGA-360 |

| 文件页数: | 8/73页 |

| 文件大小: | 929K |

| 代理商: | MPC7410THX450LE |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

16

MPC7410 RISC Microprocessor Hardware Specications

MOTOROLA

Electrical and Thermal Characteristics

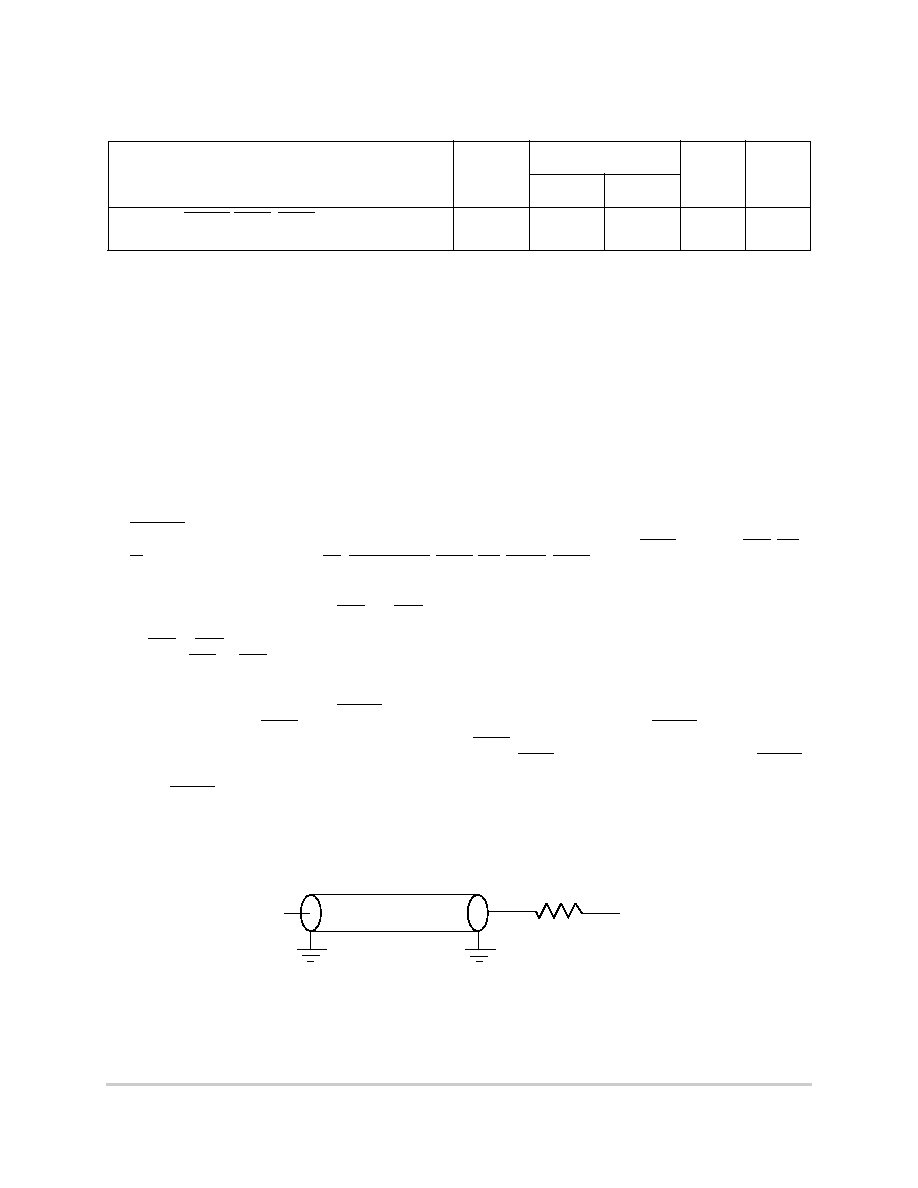

Figure 4 provides the AC test load for the MPC7410.

Figure 4. AC Test Load

SYSCLK to ARTRY, SHD0, SHD1 high impedance after

precharge

tKHARPZ

—2

t

SYSCLK

3, 8, 9

Notes:

1. All input specications are measured from the midpoint of the signal in question to the midpoint of the rising edge

of the input SYSCLK. All output specications are measured from the midpoint of the rising edge of SYSCLK to the

midpoint of the signal in question. All output timings assume a purely resistive 50-

load (see Figure 4). Input and

output timings are measured at the pin; time-of-ight delays must be added for trace lengths, vias, and connectors

in the system.

2. The symbology used for timing specications herein follows the pattern of t(signal)(state)(reference)(state) for inputs and

t(reference)(state)(signal)(state) for outputs. For example, tIVKH symbolizes the time input signals (I) reach the valid state

(V) relative to the SYSCLK reference (K) going to the high (H) state or input setup time. And tKHOV symbolizes the

time from SYSCLK(K) going high (H) until outputs (O) are valid (V) or output valid time. Input hold time can be read

as the time that the input signal (I) went invalid (X) with respect to the rising clock edge (KH)— note the position of

the reference and its state for inputs—and output hold time can be read as the time from the rising edge (KH) until

the output went invalid (OX).

3. tSYSCLK is the period of the external clock (SYSCLK) in ns. The numbers given in the table must be multiplied by

the period of SYSCLK to compute the actual time duration (in ns) of the parameter in question.

4. Includes mode select signals: BVSEL, EMODE, L2VSEL. See Figure 5 for mode select timing with respect to

HRESET.

5. All other output signals are composed of the following— A[0:31], AP[0:3], TT[0:4], TS, TBST, TSIZ[0:2], GBL, WT,

CI, DH[0:31], DL[0:31], DP[0:7], BR, CKSTP_OUT, DRDY, HIT, QREQ, RSRV.

6. Output valid time is measured from 2.4 to 0.8 V which may be longer than the time required to discharge from VDD

to 0.8 V.

7. According to the 60x bus protocol, ABB and DBB are driven only by the currently active bus master. They are

asserted low then precharged high before returning to high-Z as shown in Figure 6. The nominal precharge width

for ABB or DBB is 0.5

× t

SYSCLK, that is, less than the minimum tSYSCLK period, to ensure that another master

asserting ABB, or DBB on the following clock will not contend with the precharge. Output valid and output hold

timing is tested for the signal asserted. Output valid time is tested for precharge.The high-Z behavior is guaranteed

by design.

8. According to the 60x bus protocol, ARTRY can be driven by multiple bus masters through the clock period

immediately following AACK. Bus contention is not an issue since any master asserting ARTRY will be driving it

low. Any master asserting it low in the rst clock following AACK will then go to high-Z for one clock before

precharging it high during the second cycle after the assertion of AACK. The nominal precharge width for ARTRY

is 1.0 tSYSCLK; that is, it should be high-Z as shown in Figure 6 before the rst opportunity for another master to

assert ARTRY. Output valid and output hold timing are tested for the signal asserted. Output valid time is tested for

precharge. The high-Z behavior is guaranteed by design.

9. Guaranteed by design and not tested.

Table 8. Processor Bus AC Timing Specications 1 (continued)

At recommended operating conditions (see Table 3)

Parameter

Symbol2

400, 450, 500 MHz

Unit

Notes

Min

Max

Output

Z0 = 50

OVDD/2

RL = 50

相关PDF资料 |

PDF描述 |

|---|---|

| M48T08Y-10MH1F | 0 TIMER(S), REAL TIME CLOCK, PDSO28 |

| MK2703SILFTR | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| MC9S08RE16CFG | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 |

| MC9S08RE16CFJ | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP32 |

| MC68HC05L16FU | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC7410THX450NE | 功能描述:微处理器 - MPU NT NITCE RV1.4,1.8V -40C RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC7410THX500LE | 功能描述:微处理器 - MPU NT HITCE RV1.4 1.8V -40C RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC7410TRX400NE | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:RISC Microprocessor Hardware Specifications Addendum |

| MPC7410TRX450NE | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:RISC Microprocessor Hardware Specifications Addendum |

| MPC7410VS400LE | 功能描述:微处理器 - MPU NITRO R1.4 105C PB FREE RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

发布紧急采购,3分钟左右您将得到回复。