- 您现在的位置:买卖IC网 > PDF目录9194 > MPC9229AC (IDT, Integrated Device Technology Inc)IC CLK SYNTH LV PECL 32-LQFP PDF资料下载

参数资料

| 型号: | MPC9229AC |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 8/14页 |

| 文件大小: | 0K |

| 描述: | IC CLK SYNTH LV PECL 32-LQFP |

| 标准包装: | 250 |

| 类型: | 时钟/频率合成器 |

| PLL: | 带旁路 |

| 输入: | 晶体 |

| 输出: | LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 400MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-LQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 托盘 |

| 其它名称: | 800-2007 MPC9229ACIDT-ND |

MPC9229 REVISION 5 DECEMBER 19, 2012

3

2012 Integrated Device Technology, Inc.

MPC9229 Data Sheet

400MHZ LOW VOLTAGE PECL CLOCK SYNTHESIZER

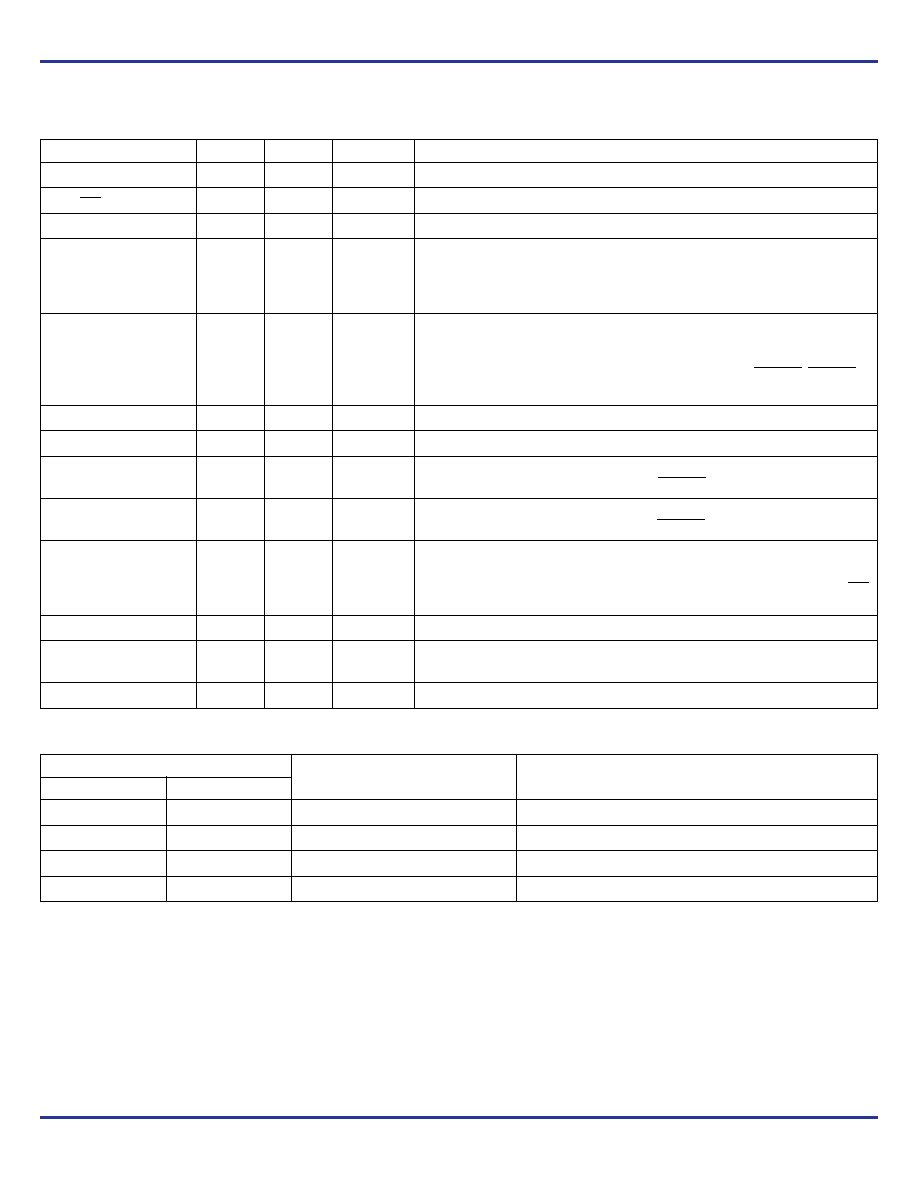

Table 1. Pin Configurations

Pin

I/O

Default

Type

Function

XTAL_IN, XTAL_OUT

—

Analog

Crystal oscillator interface

fOUT, fOUT

Output

—

LVPECL

Differential clock output

TEST

Output

—

LVCMOS

Test and device diagnosis output

S_LOAD

Input

0

LVCMOS

Serial configuration control input

This inputs controls the loading of the configuration latches with the contents of the

shift register. The latches will be transparent when this signal is high, thus the data

must be stable on the high-to-low transition

P_LOAD

Input

1

LVCMOS

Parallel configuration control input

This input controls the loading of the configuration latches with the content of the

parallel inputs (M and N). The latches will be transparent when this signal is low, thus

the parallel data must be stable on the low-to-high transition of P_LOAD. P_LOAD is

state sensitive

S_DATA

Input

0

LVCMOS

Serial configuration data input

S_CLOCK

Input

0

LVCMOS

Serial configuration clock input

M[0:8]

Input

1

LVCMOS

Parallel configuration for PLL feedback divider (M).

M is sampled on the low-to-high transition of P_LOAD.

N[1:0]

Input

1

LVCMOS

Parallel configuration for Post-PLL divider (N)

N is sampled on the low-to-high transition of P_LOAD

OE

Input

1

LVCMOS

Output enable (active high).

The output enable is synchronous to the output clock to eliminate the possibility of runt

pulses on the fOUT output. OE = L low stops fOUT in the logic low state (fOUT = L, fOUT

= H)

GND

Supply

Ground

Negative power supply (GND).

VCC

Supply

VCC

Positive power supply for I/O and core. All VCC pins must be connected to

the positive power supply for correct operation.

VCC_PLL

Supply

VCC

PLL positive power supply (analog power supply).

Table 2. Output Frequency Range and Pll Post-Divider N

N

Output Division

Output Frequency Range

1

0

0

1

200 – 400 MHz

0

1

2

100 – 200 MHz

1

0

4

50 – 100 MHz

1

8

25 – 50 MHz

相关PDF资料 |

PDF描述 |

|---|---|

| X9400WV24IZ | IC XDCP QUAD 64-TAP 10K 24-TSSOP |

| IDTQS3VH16210PAG8 | IC BUS SWITCH 20BIT HI 48-TSSOP |

| IDT5V49EE901NLGI | IC PLL CLK GEN 200MHZ 32VFQFN |

| ICS97U870AKI | IC CLK DVR PLL 1:10 40VFQFPN |

| X9250TS24Z-2.7 | IC XDCP QUAD 256TP 100K 24-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9229ACR2 | 功能描述:时钟合成器/抖动清除器 FSL 400MHz LVPECL Freq. Synthesizer RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| MPC9229EI | 功能描述:时钟合成器/抖动清除器 FSL 400MHz LVPECL Freq. Synthesizer RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| MPC9229EIR2 | 功能描述:时钟合成器/抖动清除器 FSL 400MHz LVPECL Freq. Synthesizer RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| MPC9229FA | 功能描述:IC PECL CLOCK LV 400MHZ 32-LQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MPC9229FAR2 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Synthesizer Single 32-Pin TQFP T/R |

发布紧急采购,3分钟左右您将得到回复。