- 您现在的位置:买卖IC网 > PDF目录9025 > MPC93H51ACR2 (IDT, Integrated Device Technology Inc)IC PLL CLK DRIVER LV 32-LQFP PDF资料下载

参数资料

| 型号: | MPC93H51ACR2 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 8/14页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLK DRIVER LV 32-LQFP |

| 标准包装: | 2,000 |

| 类型: | PLL 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVPECL |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:11 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 240MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-LQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 带卷 (TR) |

MPC93H51 REVISION 4 FEBRUARY 15, 2013

3

2013 Integrated Device Technology, Inc.

MPC93H51 Data Sheet

LOW VOLTAGE PLL CLOCK DRIVER

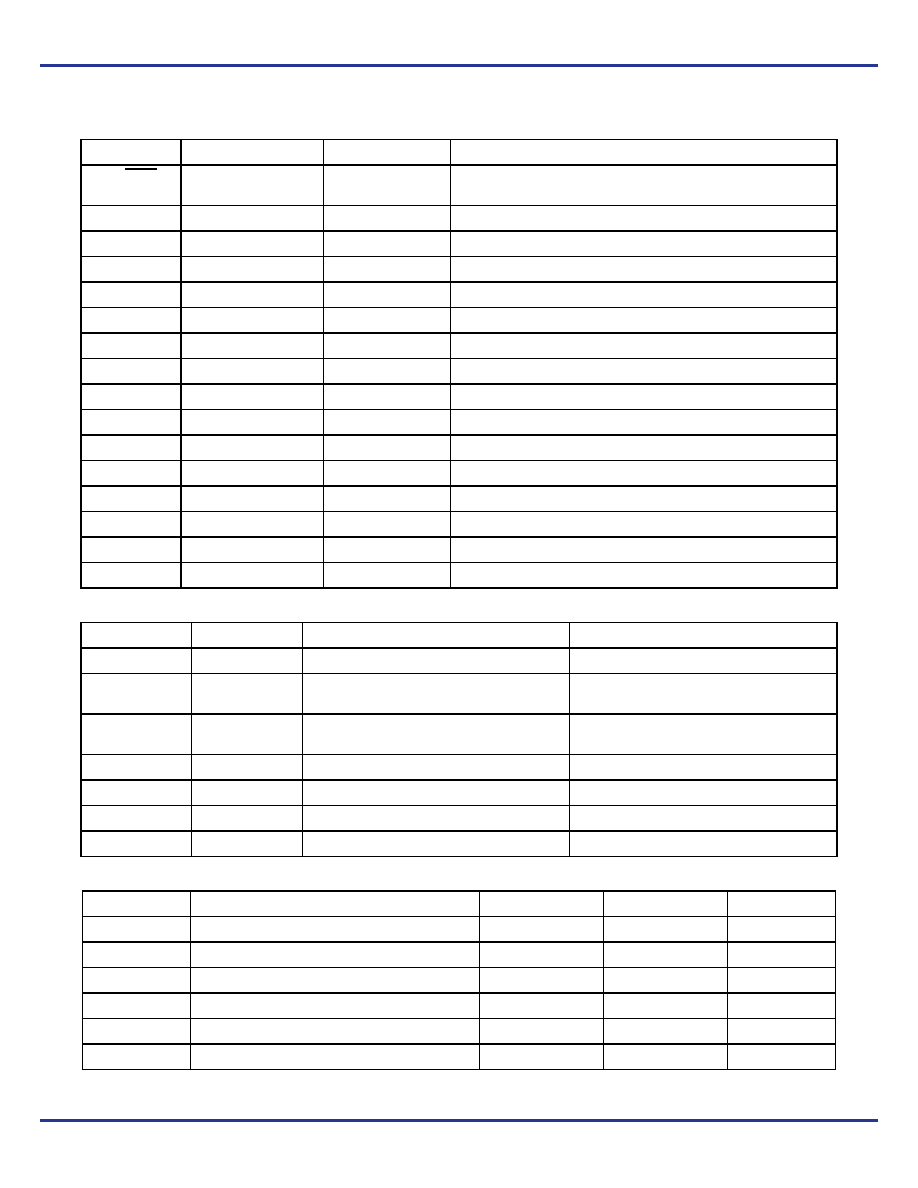

Table 1. Pin Description

Pin

I/O

Type

Function

PCLK, PCLK

Input

LVPECL

Differential clock reference

Low voltage positive ECL input

TCLK

Input

LVCMOS

Single ended reference clock signal or test clock

EXT_FB

Input

LVCMOS

Feedback signal input, connect to a QA, QB, QC, QD output

REF_SEL

Input

LVCMOS

Selects input reference clock

FSELA

Input

LVCMOS

Output A divider selection

FSELB

Input

LVCMOS

Output B divider selection

FSELC

Input

LVCMOS

Outputs C divider selection

FSELD

Input

LVCMOS

Outputs D divider selection

OE

Input

LVCMOS

Output enable/disable

QA

Output

LVCMOS

Bank A clock output

QB

Output

LVCMOS

Bank B clock output

QC0, QC1

Output

LVCMOS

Bank C clock outputs

QD0 – QD4

Output

LVCMOS

Bank D clock outputs1.5

VCCA

Supply

VCC

Positive power supply for the PLL

VCC

Supply

VCC

Positive power supply for I/O and core

GND

Supply

Ground

Negative power supply

Table 2. Function Table

Control

Default

0

1

REF_SEL

0

Selects PCLK as reference clock

Selects TCLK as reference clock

PLL_EN

1

Test mode with PLL disabled. The input clock is

directly routed to the output dividers

PLL enabled. The VCO output is routed to the

output dividers

OE

0

Outputs enabled

Outputs disabled, PLL loop is open

VCO is forced to its minimum frequency

FSELA

0

QA = VCO

2

QA = VCO

4

FSELB

0

QB = VCO

4

QB = VCO

8

FSELC

0

QC = VCO

4QC = VCO 8

FSELD

0

QD = VCO

4QD = VCO 8

Table 3. Absolute Maximum Ratings(1)

Symbol

Characteristics

Min

Max

Unit

VCC

Supply Voltage

–0.3

3.9

V

VIN

DC Input Voltage

–0.3

VCC+0.3

V

VOUT

DC Output Voltage

–0.3

VCC+0.3

V

IIN

DC Input Current

20

mA

IOUT

DC Output Current

50

mA

TS

Storage Temperature

–65

150

C

相关PDF资料 |

PDF描述 |

|---|---|

| MPC9351FAR2 | IC PLL CLOCK DRIVER LV 32-LQFP |

| VE-B3D-MV-F1 | CONVERTER MOD DC/DC 85V 150W |

| VE-B3B-MV-F4 | CONVERTER MOD DC/DC 95V 150W |

| MPC9351ACR2 | IC PLL CLOCK DRIVER LV 32-LQFP |

| IDT23S09E-1HPGGI8 | IC CLK BUFFER ZD HI DRV 16-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC93H51FA | 功能描述:IC PLL CLK DVR HI-DRIVE 32-LQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MPC93H52AC | 功能描述:时钟发生器及支持产品 FSL 1-11 LVCMOS PLL Clock Generator, hig RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC93H52ACR2 | 功能描述:IC CLK GEN ZD 1:11 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| MPC93H52FA | 功能描述:IC CLOCK GEN/DVR HI-DRIVE 32LQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MPC93H52FAR2 | 制造商:Integrated Device Technology Inc 功能描述:ZERO DLY PLL CLOCK GEN SGL 32LQFP - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。