- 您现在的位置:买卖IC网 > PDF目录45376 > MPM22CGA850B (INTEL CORP) 32-BIT, 850 MHz, MICROPROCESSOR, XMA PDF资料下载

参数资料

| 型号: | MPM22CGA850B |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 850 MHz, MICROPROCESSOR, XMA |

| 封装: | MMC-2 |

| 文件页数: | 8/68页 |

| 文件大小: | 966K |

| 代理商: | MPM22CGA850B |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

Pentium

III Processor Mobile Module MMC-2

Featuring Intel

SpeedStep Technology

10

Datasheet

243356-006

3.1.4

PCI Signals

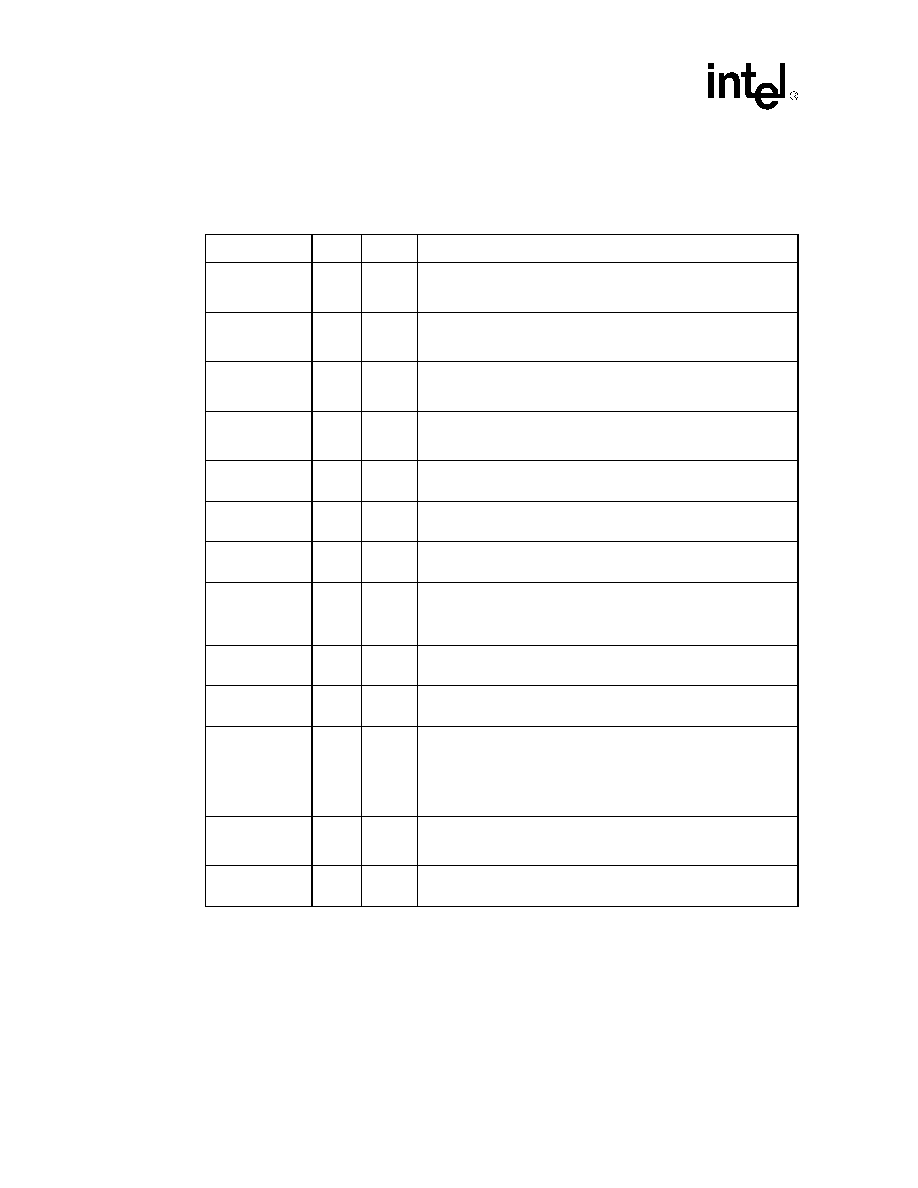

Table 4 provides descriptions of the PCI signals.

Table 4.

PCI Signal Descriptions

Name

Type

Voltage

Description

AD[31:0]

I/O

PCI

V_3

Address/Data: The standard PCI address and data lines. The

address is driven with FRAME# assertion, and data is driven or

received in the following clocks.

C/BE[3:0]

I/O

PCI

V_3

Command/Byte Enable: The command is driven with FRAME#

assertion, and byte enables corresponding to supplied or requested

data are driven on the following clocks.

FRAME#

I/O

PCI

V_3

Frame: Assertion indicates the address phase of a PCI transfer.

Negation indicates that the cycle initiator desires one more data

transfer.

DEVSEL#

I/O

PCI

V_3

Device Select: The 82443BX Host Bridge drives this signal when a

PCI initiator is attempting to access DRAM. DEVSEL# is asserted at

medium decode time.

IRDY#

I/O

PCI

V_3

Initiator Ready: Asserted when the initiator is ready for a data

transfer.

TRDY#

I/O

PCI

V_3

Target Ready: Asserted when the target is ready for a data transfer.

STOP#

I/O

PCI

V_3

Stop: Asserted by the target to request the master to stop the current

transaction.

PLOCK#

I/O

PCI

V_3

Lock: Indicates an exclusive bus operation and may require multiple

transactions to complete. When LOCK# is asserted, nonexclusive

transactions may proceed. The 82443BX supports lock for CPU

initiated cycles only. PCI initiated locked cycles are not supported.

REQ[4:0]#

I

PCI

V_3

PCI Request: PCI master requests for the PCI.

GNT[4:0]#

O

PCI

V_3

PCI Grant: Permission is given to the master to use PCI.

PHOLD#

I

PCI

V_3

PCI Hold: This signal comes from the expansion bridge. It is the

bridge request for PCI. The 82443BX Host Bridge will drain the DRAM

write buffers, drain the processor-to-PCI posting buffers, and acquire

the host bus before granting the request via PHLDA#. This ensures

that GAT timing is met for ISA masters. The PHOLD# protocol has

been modified to include support for passive release.

PHLDA#

O

PCI

V_3

PCI Hold Acknowledge: This signal is driven by the 82443BX Host

Bridge to grant PCI to the expansion bridge. The PHLDA# protocol

has been modified to include support for passive release.

PAR

I/O

PCI

V_3

Parity: A single parity bit is provided over AD[31:0] and C/BE[3:0]#.

相关PDF资料 |

PDF描述 |

|---|---|

| MPM22CGC600A | 32-BIT, 600 MHz, MICROPROCESSOR, XMA |

| MPM22CGA800A | 32-BIT, 800 MHz, MICROPROCESSOR, XMA |

| MPM22PDA266B | 32-BIT, 266 MHz, MICROPROCESSOR, XMA |

| MPM22PDA366B | 32-BIT, 366 MHz, MICROPROCESSOR, XMA |

| MPM22PDA266A | 32-BIT, 266 MHz, MICROPROCESSOR, XMA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPM-25S | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

| MPM-25S-05 | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

| MPM-25S-12 | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

| MPM-25S-15 | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

| MPM-25S-24 | 制造商:MPD 制造商全称:MicroPower Direct, LLC 功能描述:Universal Input, 25W Miniature, PC Mount AC/DC Power Supplies |

发布紧急采购,3分钟左右您将得到回复。