- 您现在的位置:买卖IC网 > PDF目录80343 > MQ80C52CXXX-20SBR (ATMEL CORP) 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 PDF资料下载

参数资料

| 型号: | MQ80C52CXXX-20SBR |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 |

| 封装: | CERAMIC, QFP-44 |

| 文件页数: | 2/32页 |

| 文件大小: | 3152K |

| 代理商: | MQ80C52CXXX-20SBR |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

10

7707F–AVR–11/10

AT90USB82/162

conditional operations. Note that the Status Register is updated after all ALU operations, as

specified in the Instruction Set Reference. This will in many cases remove the need for using the

dedicated compare instructions, resulting in faster and more compact code.

The Status Register is not automatically stored when entering an interrupt routine and restored

when returning from an interrupt. This must be handled by software.

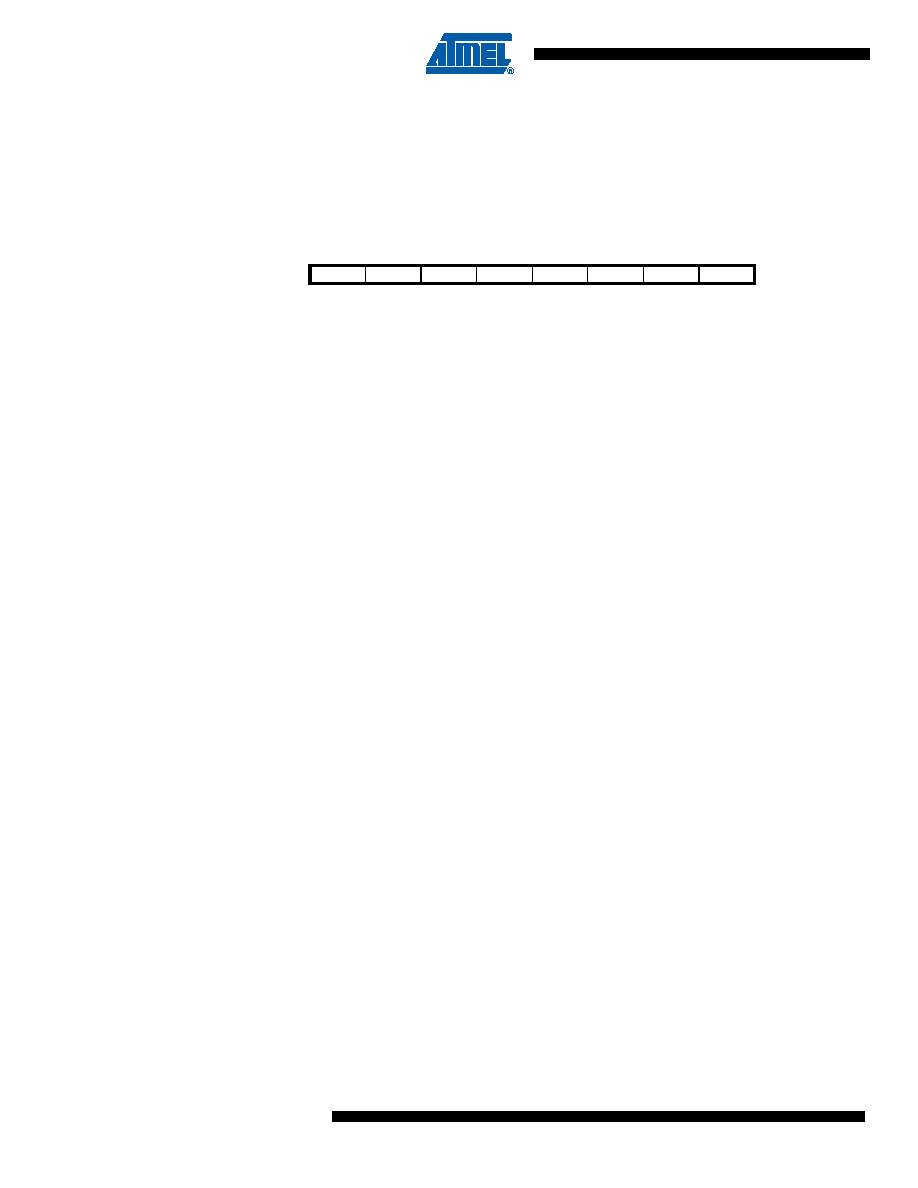

The AVR Status Register – SREG – is defined as:

Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual inter-

rupt enable control is then performed in separate control registers. If the Global Interrupt Enable

Register is cleared, none of the interrupts are enabled independent of the individual interrupt

enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by

the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared by

the application with the SEI and CLI instructions, as described in the instruction set reference.

Bit 6 – T: Bit Copy Storage

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or desti-

nation for the operated bit. A bit from a register in the Register File can be copied into T by the

BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the

BLD instruction.

Bit 5 – H: Half Carry Flag

The Half Carry Flag H indicates a Half Carry in some arithmetic operations. Half Carry Is useful

in BCD arithmetic. See the “Instruction Set Description” for detailed information.

Bit 4 – S: Sign Bit, S = N

⊕ V

The S-bit is always an exclusive or between the Negative Flag N and the Two’s Complement

Overflow Flag V. See the “Instruction Set Description” for detailed information.

Bit 3 – V: Two’s Complement Overflow Flag

The Two’s Complement Overflow Flag V supports two’s complement arithmetics. See the

“Instruction Set Description” for detailed information.

Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See the

“Instruction Set Description” for detailed information.

Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the “Instruction

Set Description” for detailed information.

Bit 0 – C: Carry Flag

The Carry Flag C indicates a carry in an arithmetic or logic operation. See the “Instruction Set

Description” for detailed information.

Bit

7

65

43

21

0

IT

H

S

V

N

Z

C

SREG

Read/Write

R/W

Initial Value

0

相关PDF资料 |

PDF描述 |

|---|---|

| MD80C32E-30/883D | 8-BIT, 30 MHz, MICROCONTROLLER, CDIP40 |

| MQ80C32E-30SB | 8-BIT, 30 MHz, MICROCONTROLLER, CQFP44 |

| MQ80C52XXX-30SC | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, CQFP44 |

| MR80C154-12P883 | 8-BIT, 12 MHz, MICROCONTROLLER, CQCC44 |

| MPC750ARX266LHR2 | 32-BIT, 266 MHz, RISC PROCESSOR, CBGA255 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MQ82370-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MQ8238020 | 制造商:Intel 功能描述:CONTROLLER: OTHER |

| MQ82380-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MQ82380-20/R | 制造商:Rochester Electronics LLC 功能描述: |

| MQ82592 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。