- 您现在的位置:买卖IC网 > PDF目录25626 > MQ80C52TXXX-20/883D (ATMEL CORP) 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 PDF资料下载

参数资料

| 型号: | MQ80C52TXXX-20/883D |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 |

| 封装: | CERAMIC, QFP-44 |

| 文件页数: | 13/28页 |

| 文件大小: | 6193K |

| 代理商: | MQ80C52TXXX-20/883D |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

20

2467X–AVR–06/11

ATmega128

Data Memory Access

Times

This section describes the general access timing concepts for internal memory access. The

internal data SRAM access is performed in two clk

CPU cycles as described in Figure 10.

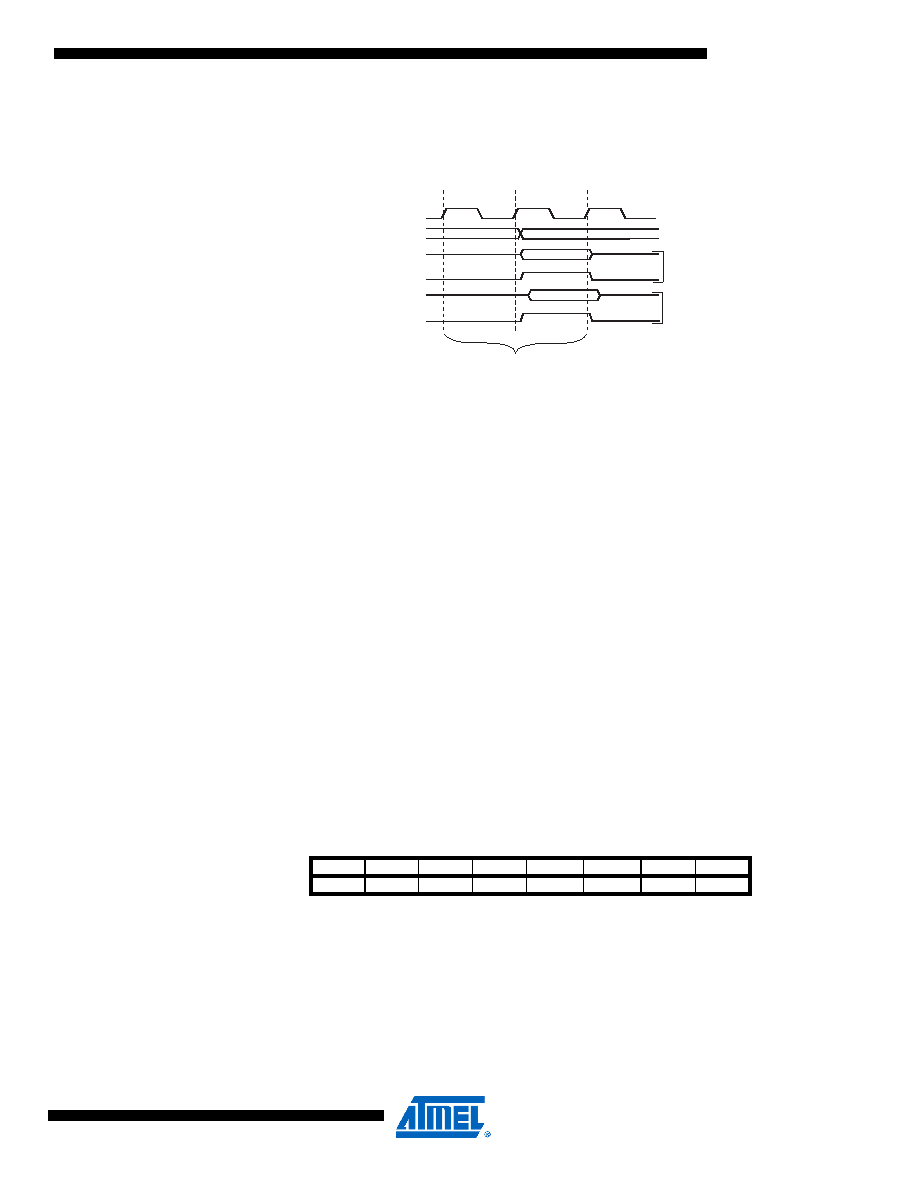

Figure 10. On-chip Data SRAM Access Cycles

EEPROM Data

Memory

The Atmel AVRATmega128 contains 4Kbytes of data EEPROM memory. It is organized as a

separate data space, in which single bytes can be read and written. The EEPROM has an

endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the

CPU is described in the following, specifying the EEPROM Address Registers, the EEPROM

Data Register, and the EEPROM Control Register.

“Memory Programming” on page 286 contains a detailed description on EEPROM programming

in SPI, JTAG, or Parallel Programming mode

EEPROM Read/Write

Access

The EEPROM access registers are accessible in the I/O space.

The write access time for the EEPROM is given in Table 2. A self-timing function, however, lets

the user software detect when the next byte can be written. If the user code contains instructions

that write the EEPROM, some precautions must be taken. In heavily filtered power supplies, V

CC

is likely to rise or fall slowly on Power-up/down. This causes the device for some period of time

to run at a voltage lower than specified as minimum for the clock frequency used. See “Prevent-

ing EEPROM Corruption” on page 24. for details on how to avoid problems in these situations.

In order to prevent unintentional EEPROM writes, a specific write procedure must be followed.

Refer to the description of the EEPROM Control Register for details on this.

When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is

executed. When the EEPROM is written, the CPU is halted for two clock cycles before the next

instruction is executed.

EEPROM Address

Register – EEARH and

EEARL

Bits 15..12 – Res: Reserved Bits

These are reserved bits and will always read as zero. When writing to this address location,

write these bits to zero for compatibility with future devices.

clk

WR

RD

Data

Address

Address valid

T1

T2

T3

Compute Address

Read

Write

CPU

Memory access instruction

Next instruction

Bit

15141312

11

10

9

8

–

EEAR11

EEAR10

EEAR9

EEAR8

EEARH

EEAR7

EEAR6

EEAR5

EEAR4

EEAR3

EEAR2

EEAR1

EEAR0

EEARL

7

654

3

2

1

0

Read/Write

RR

R/W

Initial Value

0

X

XXX

X

相关PDF资料 |

PDF描述 |

|---|---|

| MD80C32-30P883 | 8-BIT, 30 MHz, MICROCONTROLLER, CDIP40 |

| MD83C154DXXX-12/883 | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| MD83C154CXXX-16/883D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| MR83C154DTXXX-16P883 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQCC44 |

| MR80C32E-20/883R | 8-BIT, 20 MHz, MICROCONTROLLER, CQCC44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MQ82370-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MQ8238020 | 制造商:Intel 功能描述:CONTROLLER: OTHER |

| MQ82380-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MQ82380-20/R | 制造商:Rochester Electronics LLC 功能描述: |

| MQ82592 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。