- 您现在的位置:买卖IC网 > PDF目录80502 > MSM80C35RS (OKI ELECTRIC INDUSTRY CO LTD) 8-BIT, 11 MHz, MICROCONTROLLER, PDIP40 PDF资料下载

参数资料

| 型号: | MSM80C35RS |

| 厂商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 11 MHz, MICROCONTROLLER, PDIP40 |

| 封装: | 0.600 INCH, 2.54 MM PITCH, PLASTIC, DIP-40 |

| 文件页数: | 2/20页 |

| 文件大小: | 149K |

| 代理商: | MSM80C35RS |

10/20

Semiconductor

MSM80C48/49/50, MSM80C35/39/40

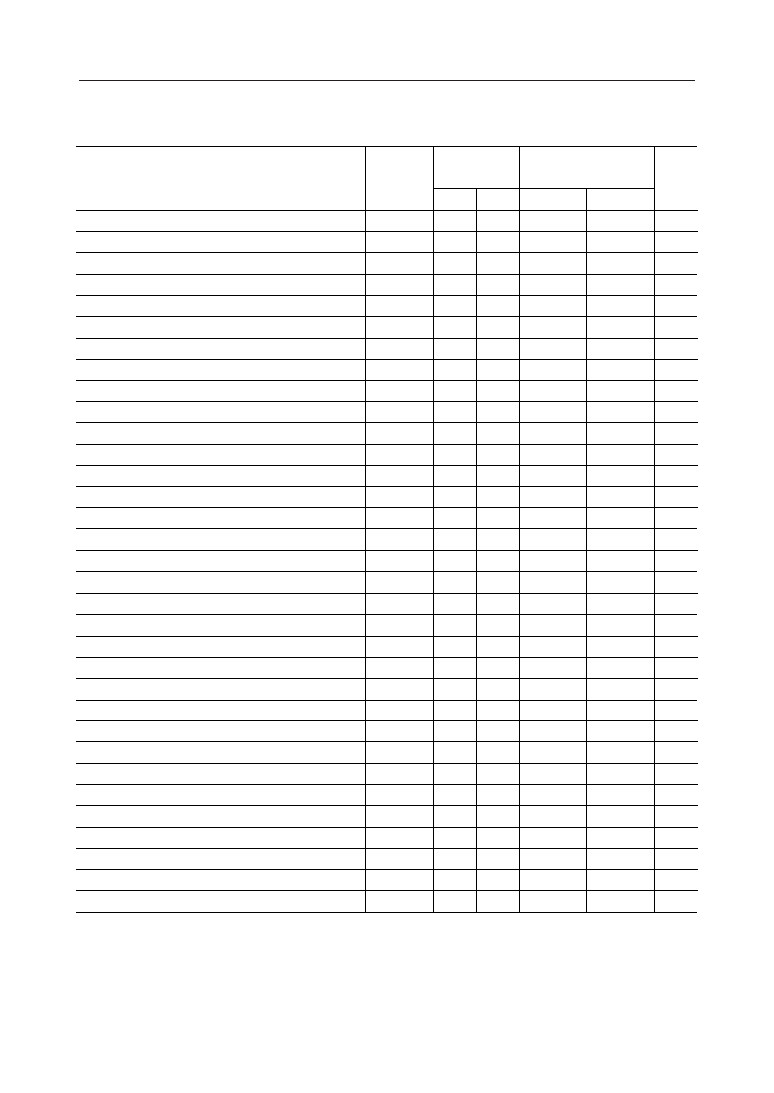

AC Characteristics

Parameter

Symbol

VCC=5 V±10%

11 MHz Clock

Variable clock

0 to 11 MHz

Unit

Min.

Max.

Min.

Max.

ALE Pulse Width

tLL

150

—

3.5t–170

—

ns

Address Setup Time (up to ALE)

tAL

70

—

2t–110

—

ns

Address Hold Time (from ALE)

tLA

50

—

t–40

—

ns

Bus Port Latch Data Setup Time (up to ALE Rising Edge)

tBL

110

—

2.5t –115

—

ns

Bus Port Latch Data Hold Time (from ALE Rising Edge)

tLB

90

—

1.5 t–45

—

ns

Control Pulse Width (RD, WR)

tCC1

480

—

7t–155

—

ns

Data Setup Time (before WR)

tDW

390

—

6t–155

—

ns

Data Hold after Time (after WR)

tWD

40

—

2t–140

—

ns

Data Hold Time (after RD, PSEN)

tDR

0

110

0

1.5t–30

ns

PSEN to Data-in

tRD2

—

190

—

5t–265

ns

Address Setup to WR

tAW

300

—

6t–245

—

ns

Address Setup to Data-in

tAD1

—

730

—

12t–360

ns

Address Float to PSEN

tAFC2

10

—

10

—

ns

PROG to Input Data Valid

tPR

—

650

—

9t–170

ns

Input Data Hold Time

tPF

0

140

0

1.5t

ns

Output Data Setup Time

tDP

250

—

6t–290

—

ns

Output Data Hold Time

tPD

40

—

3t–230

—

ns

PROG Pulse Width

tPP

700

—

10t–210

—

ns

Port 2 I/O Setup Time

tPL

160

—

4.5–250

—

ns

Port 2 I/O Hold Time

tLP

15

—

1.5t–120

—

ns

(VCC=2.5V to 6V (*1), Ta=–40 to +85°C)

Control Pulse Width (PSEN)

tCC2

350

—

6t–200

—

ns

RD to Data-in

tRD1

—

350

—

5t–265

ns

Address Setup to Instruction

tAD2

—

460

—

8t–265

ns

Address Float to RD, WR

tAFC1

140

—

2t–40

—

ns

Port Control Setup Time (up to PROG Falling Edge)

tCP

50

—

2t–130

—

ns

Control Pulse Setup Time from ALE (PSEN)

tLAFC2

60

—

t–30

—

ns

Control Pulse Setup Time from ALE (RD, WR)

tLAFC1

200

—

3t–75

—

ns

Control Pulse up to ALE (RD, WR, PROG)

tCA1

50

—

1.5t–85

—

ns

Control Pulse up to ALE (PSEN)

tCA2

320

—

4.5t–90

—

ns

Port Control Hold Time (from PROG Falling Edge)

tPC

100

—

4t–260

—

ns

Port Output Data (from ALE)

tPV

—

510

—

4t+145

ns

T0 Cycle

tOPRR

270

—

3t

—

ns

Instruction Execution Time

tCY

1.36

—

15t

—

ms

Note : Control output : CL=80pF

Bus output : CL=150pF [for 20 pF (tAL, tAFC1, tAFC2)]

*1 Minimum operating voltage is dependent on frequency.

相关PDF资料 |

PDF描述 |

|---|---|

| MPC8536AVTAVLA | 32-BIT, 1500 MHz, MICROPROCESSOR, PBGA783 |

| MB95F416KPMC-G-SNE2 | MICROCONTROLLER, PQFP80 |

| MC9S08SG16E1VTJR | MICROCONTROLLER, PDSO16 |

| M37480M4-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO32 |

| M37481M8T-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MSM80C39 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS 8-Bit Microcontroller |

| MSM80C40 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS 8-Bit Microcontroller |

| MSM80C48 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS 8-Bit Microcontroller |

| MSM80C49 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS 8-Bit Microcontroller |

| MSM80C49-628RS | 制造商:OK International 功能描述: |

发布紧急采购,3分钟左右您将得到回复。