- 您现在的位置:买卖IC网 > PDF目录80401 > MSM80C40RS (OKI ELECTRIC INDUSTRY CO LTD) 8-BIT, 6 MHz, MICROCONTROLLER, PDIP40 PDF资料下载

参数资料

| 型号: | MSM80C40RS |

| 厂商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 6 MHz, MICROCONTROLLER, PDIP40 |

| 封装: | 0.600 INCH, 2.54 MM PITCH, PLASTIC, DIP-40 |

| 文件页数: | 15/20页 |

| 文件大小: | 149K |

| 代理商: | MSM80C40RS |

4/20

Semiconductor

MSM80C48/49/50, MSM80C35/39/40

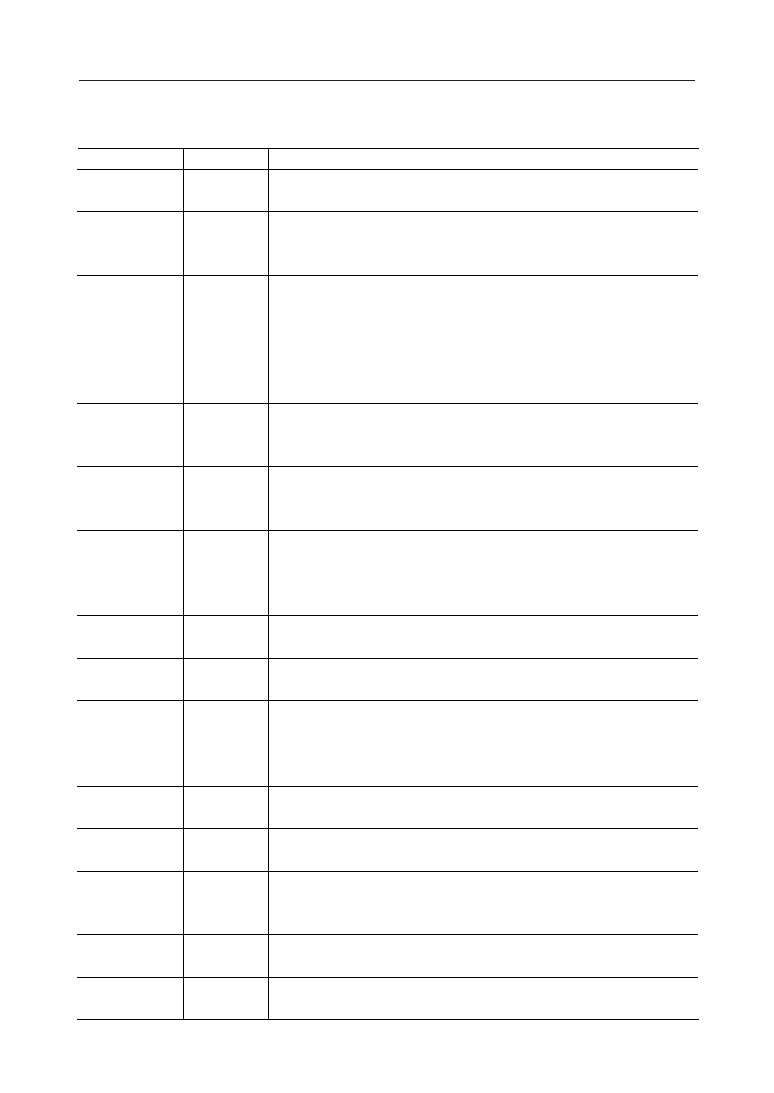

PIN DESCRIPTIONS

Symbol

Type

Description

P10-P17

(PORT 1)

8-bit quasi-bidirectional port

I/O

P20-P27

(PORT 2)

8-bit quasi-bidirectional port

The high-order four bits of external program memory addresses can be output

from P2.0-P2.3, to which the I/O expander MSM82C43RS may also be connected.

I/O

DB0-DB7

(BUS)

Bidirectional port

The low-order eight bits of external program memory address can be output

from this port, and the addressed instruction is fetched under the control of

PSEN signal. Also, the external data memory address is output, and data is

read and written synchronously using RD and WR signals.

The port can also serve as either a statically latched output port or a

non-latching input port.

I/O

T0

(Test 0)

The input can be tested with the conditional jump instructions JT0 and JNT0.

The execution of the ENT0 CLK instruction causes a clock output.

I/O

T1

(Test 1)

The input can be tested with the conditional jump instructions JT1 and JNT1.

The execution of a STRT CNT instruction causes an internal counter input.

I

INT

(Interrupt)

Interrupt input. If interrupt is enabled, INT input initiates an interrupt.

Interrupt is disabled after a reset.

Also testable with a JNI instruction. Can be used to terminate the power-down

mode. (Active "0" level)

I

RD

(Read)

A signal to read data from external data memory. (Active "0" level)

O

WR

(Write)

A signal to write data to external data memory. (Active "0" level)

O

ALE

Address &

Data Latch

Clock

This signal is generated in each cycle. It may be used as a clock output.

External data memory or external program memory is addressed upon the

falling edge. For the external ROM, this signal is used to latch the bus port data

upon the ALE signal rise-up after the execution of the OUTL BUS, A instruction.

O

PSEN Program

Store Enable

A signal to fetch an instruction from external program memory

(Active "0" level)

O

RESET

RESET input initialize the processor. (Active "0" level)

Used to terminate the power-down mode.

I

SS

(Single Step)

A program is executed step by step. This pin can also be used to control

internal oscillation when the power-down mode is reset.

(Active "0" level)

I

EA

(External Access)

When held at high level, all instructions are fetched from external memory.

(Active "1" level)

I

PROG

(Expander Strobe)

This output strobes the MSM82C43RS I/O expander.

O

相关PDF资料 |

PDF描述 |

|---|---|

| MSM82C59A-2JS | 80C85AH; 80C86A; 80C88A COMPATIBLE, INTERRUPT CONTROLLER, PQCC28 |

| MPC8536CVTAQGA | 32-BIT, 1000 MHz, MICROPROCESSOR, PBGA783 |

| MB96F313RSBPMC-GSE1 | 16-BIT, FLASH, 56 MHz, MICROCONTROLLER, PQFP48 |

| MC9S08SG16E1VTG | MICROCONTROLLER, PDSO16 |

| M37920FGMHP | 16-BIT, FLASH, 26 MHz, MICROCONTROLLER, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MSM80C48 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS 8-Bit Microcontroller |

| MSM80C49 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS 8-Bit Microcontroller |

| MSM80C49-628RS | 制造商:OK International 功能描述: |

| MSM80C50 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS 8-Bit Microcontroller |

| MSM80C51F | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS 8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。