- 您现在的位置:买卖IC网 > PDF目录299520 > MSM82C53-2JS (OKI SEMICONDUCTOR CO., LTD.) CMOS PROGRAMMABLE INTERVAL TIMER PDF资料下载

参数资料

| 型号: | MSM82C53-2JS |

| 厂商: | OKI SEMICONDUCTOR CO., LTD. |

| 元件分类: | 定时器 |

| 英文描述: | CMOS PROGRAMMABLE INTERVAL TIMER |

| 中文描述: | CMOS可编程间隔计时器 |

| 文件页数: | 19/19页 |

| 文件大小: | 149K |

| 代理商: | MSM82C53-2JS |

9/19

Semiconductor

MSM82C53-2RS/GS/JS

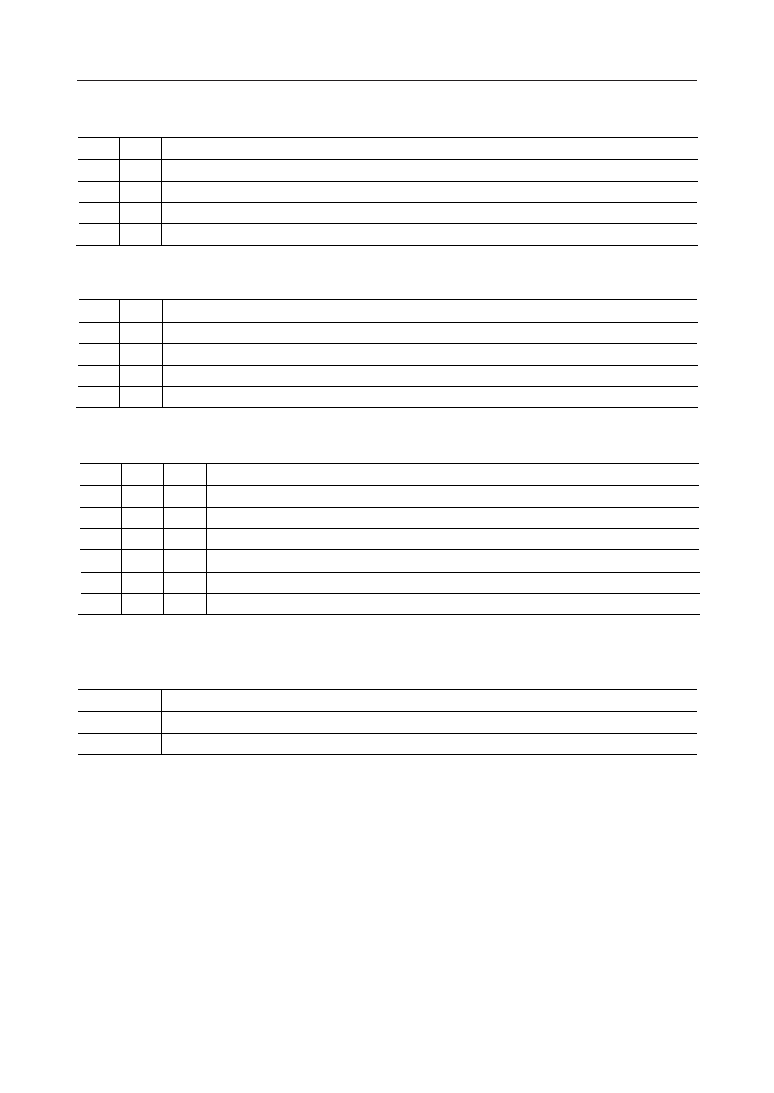

Select Counter (SC0, SC1):

Selection of set counter

Read/Load (RL1, RL0):

Count value Reading/Loading format setting

Mode (M2, M1, M0):

Operation waveform mode setting

0

0

M2

Set Contents

0

1

0

M1

1

0

1

0

M0

1

0

1

Mode 0 (Interrupt on Terminal Count)

Mode 1 (Programmable One-Shot)

Mode 2 (Rate Generator)

Mode 3 (Square Wave Generator)

Mode 4 (Software Triggered Strobe)

Mode 5 (Hardware Triggered Strobe)

denotes "not specified".

BCD:

Operation count mode setting

1

0

BCD

Binary Count (16-bit Binary)

BCD Count (4-decade Binary Coded Decimal)

Set Contents

After setting Read/Load, Mode, and BCD in each counter as outlined above, next set the desired

count value. (In some Modes, counting is started immediately after the count value has been

written). This count value setting must conform with the Read/Load format set in advance.

Note that the internal counters are reset to 0000H during control word setting. The counter

value (0000H) can’t be read.

If the two bytes (LSB and MSB) are written at this stage (RL0 and RL1 = 1,1), take note of the

following precaution.

Although the count values may be set in the three counters in any sequence after the control

word has been set in each counter, count values must be set consecutively in the LSB - MSB order

in any one counter.

0

1

0

SC1

1

0

1

0

SC0

Counter #0 Selection

Counter #1 Selection

Counter #2 Selection

Illegal Combination

Set Contents

0

1

0

RL1

Set Contents

1

0

1

0

RL0

Counter Latch Operation

Reading/Loading of Least Significant Byte (LSB)

Reading/Loading of Most Significant Byte (MSB)

Reading/Loading of LSB Followed by MSB

相关PDF资料 |

PDF描述 |

|---|---|

| MSM82C53-2RS | CMOS PROGRAMMABLE INTERVAL TIMER |

| MSM82C53-2xx | CMOS PROGRAMMABLE INTERVAL TIMER |

| MSM82C54-2GS | CMOS PROGRAMMABLE INTERVAL TIMER |

| MSM82C54-2JS | CMOS PROGRAMMABLE INTERVAL TIMER |

| MSM82C54-2RS | CMOS PROGRAMMABLE INTERVAL TIMER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MSM82C53-2RS | 制造商:ROHM Semiconductor 功能描述: |

| MSM82C53-2XX | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS PROGRAMMABLE INTERVAL TIMER |

| MSM82C54-2GS | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:CMOS PROGRAMMABLE INTERVAL TIMER |

| MSM82C54-2J3 | 制造商:OKI Semiconductor 功能描述:CPU I/OS EOL311208 制造商:ROHM Semiconductor 功能描述: |

| MSM82C54-2JS | 制造商:ROHM Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。