- 您现在的位置:买卖IC网 > PDF目录385640 > MT4LC16M4T8TG-5S (Micron Technology, Inc.) DRAM PDF资料下载

参数资料

| 型号: | MT4LC16M4T8TG-5S |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | DRAM |

| 中文描述: | 内存 |

| 文件页数: | 1/20页 |

| 文件大小: | 350K |

| 代理商: | MT4LC16M4T8TG-5S |

1

16 Meg x 4 FPM DRAM

D21_2.p65 – Rev. 5/00

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2000, Micron Technology, Inc.

16 MEG x 4

FPM DRAM

FEATURES

Single +3.3V ±0.3V power supply

Industry-standard x4 pinout, timing, functions,

and packages

13 row, 11 column addresses (A7)

12 row, 12 column addresses (T8)

High-performance CMOS silicon-gate process

All inputs, outputs and clocks are LVTTL-compat-

ible

FAST-PAGE-MODE (FPM) access

4,096-cycle CAS#-BEFORE-RAS# (CBR) REFRESH

distributed across 64ms

Optional self refresh (S) for low-power data

retention

OPTIONS

Refresh Addressing

4,096 (4K) rows

8,192 (8K) rows

MARKING

T8

A7

Plastic Packages

32-pin SOJ (400 mil)

32-pin TSOP (400 mil)

DJ

TG

Timing

50ns access

60ns access

-5

-6

Refresh Rates

Standard Refresh

Self Refresh (128ms period)

None

S*

NOTE:

1. The 16 Meg x 4 FPM DRAM base number

differentiates the offerings in one place—

MT4LC16M4A7. The fifth field distinguishes

various options: A7 designates an 8K refresh and

T8 designates a 4K refresh for FPM DRAMs.

2. The # symbol indicates signal is active LOW.

*Contact factory for availability

Part Number Example:

MT4LC16M4A7DJ

DRAM

MT4LC16M4A7, MT4LC16M4T8

www.micronsemi.com/mti/msp/html/datasheet.htmlKEY TIMING PARAMETERS

SPEED

-5

-6

t

RC

90ns

110ns

t

RAC

50ns

60ns

t

PC

30ns

35ns

t

AA

25ns

30ns

t

CAC

13ns

15ns

16 MEG x 4 FPM DRAM PART NUMBERS

REFRESH

ADDRESSING PACKAGE

8K

8K

8K

8K

4K

4K

4K

4K

PART NUMBER

MT4LC16M4A7DJ-x

MT4LC16M4A7DJ-x S

MT4LC16M4A7TG-x

MT4LC16M4A7TG-x S

MT4LC16M4T8DJ-x

MT4LC16M4T8DJ-x S

MT4LC16M4T8TG-x

MT4LC16M4T8TG-x S

REFRESH

Standard

Self

Standard

Self

Standard

Self

Standard

Self

SOJ

SOJ

TSOP

TSOP

SOJ

SOJ

TSOP

TSOP

x = speed

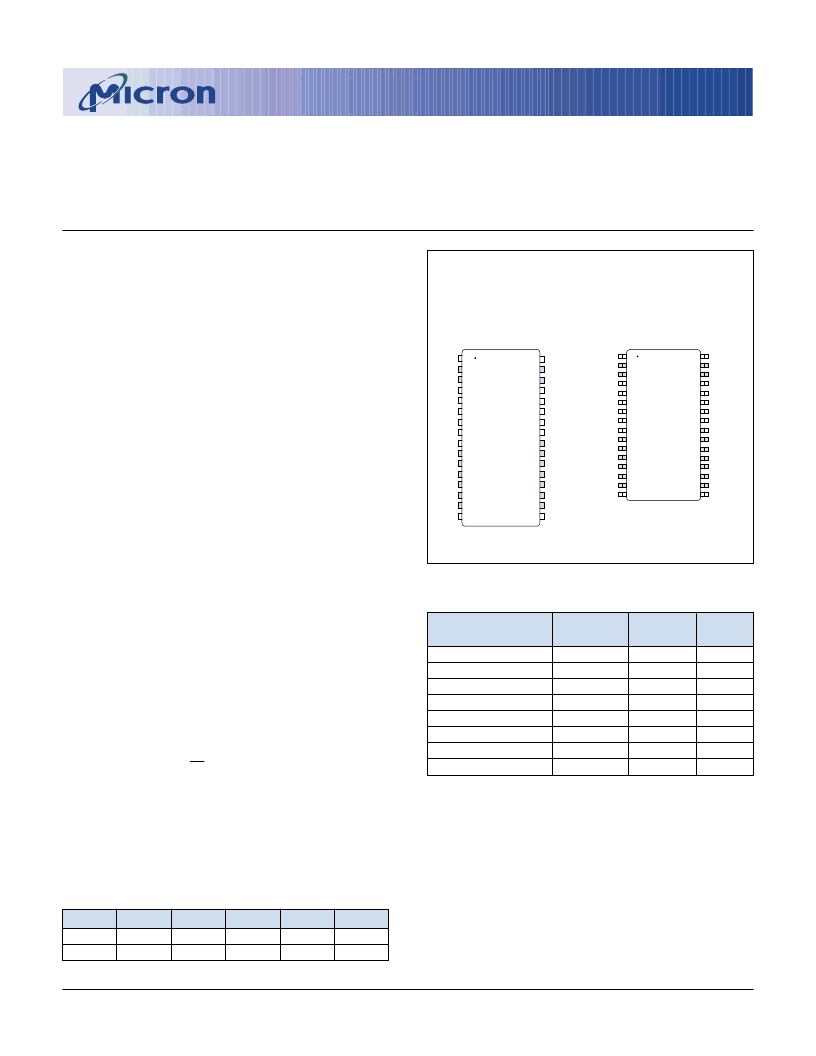

32-Pin TSOP

32-Pin SOJ

PIN ASSIGNMENT (Top View )

V

CC

DQ0

DQ1

NC

NC

NC

NC

WE#

RAS#

A0

A1

A2

A3

A4

A5

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

V

SS

DQ3

DQ2

NC

NC

NC

CAS#

OE#

A12

/NC**

A11

A10

A9

A8

A7

A6

V

SS

**A12 on A7 version and NC on T8 version

V

CC

DQ0

DQ1

NC

NC

NC

NC

WE#

RAS#

A0

A1

A2

A3

A4

A5

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

V

SS

DQ3

DQ2

NC

NC

NC

CAS#

OE#

A12

/NC**

A11

A10

A9

A8

A7

A6

V

SS

GENERAL DESCRIPTION

The 16 Meg x 4 DRAMs are high-speed CMOS,

dynamic random-access memory devices contain-ing

67,108,864 bits organized in a x4 configuration. The

MT4LC16M4A7 and MT4LC16M4T8 are functionally

organized as 16,777,216 locations containing four bits

each. The 16,777,216 memory locations are arranged in

8,192 rows by 2,048 columns for the MT4LC16M4A7 or

4,096 rows by 4,096 columns for the MT4LC16M4T8.

During READ or WRITE cycles, each location is uniquely

相关PDF资料 |

PDF描述 |

|---|---|

| MT4LC16M4T8TG-6 | DRAM |

| MT4LC16M4T8TG-6S | DRAM |

| MT4LC4M16F5 | DRAM |

| MT4LC4M16R6 | DRAM |

| MT4LC8M8E1TG-5 | DRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT4LC16M4T8TG-6 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DRAM |

| MT4LC16M4T8TG-6S | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DRAM |

| MT4LC1M16C3DJ-6 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:FPM DRAM |

| MT4LC1M16C3DJ-6S | 制造商:MICRON 制造商全称:Micron Technology 功能描述:FPM DRAM |

| MT4LC1M16C3TG6 | 制造商:Micron Technology Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。