- 您现在的位置:买卖IC网 > PDF目录10497 > MX7705EPE+ (Maxim Integrated Products)IC ADC 16BIT 2CH 16-DIP PDF资料下载

参数资料

| 型号: | MX7705EPE+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 21/33页 |

| 文件大小: | 0K |

| 描述: | IC ADC 16BIT 2CH 16-DIP |

| 产品培训模块: | MAX11200 ADC Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 25 |

| 位数: | 16 |

| 采样率(每秒): | 500 |

| 数据接口: | MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 16-DIP(0.300",7.62mm) |

| 供应商设备封装: | 16-PDIP |

| 包装: | 管件 |

| 输入数目和类型: | 2 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

MX7705

Using FSYNC

When FSYNC = 1, the digital filter and analog modula-

tor are in a reset state, inhibiting normal operation. Set

FSYNC = 0 to begin calibration or conversion.

When configured for normal operation (MD0 and MD1

set to 0), DRDY goes low 3 x 1/output data rate after

FSYNC goes low to indicate that the new conversion

result is ready to be read from the data register. DRDY

returns high when a read operation on the data register

is complete. As long as FSYNC remains low, the

MX7705 performs free-running conversions with the

data registers updating at the output data rate. If the

valid data is not read before the next conversion result

is ready, DRDY returns high for 500 x 1/fCLKIN before

going low again to indicate a new conversion. Set

FSYNC = 1 to stop converting data.

If FSYNC goes high while DRDY is low (indicating that

valid data has not yet been read from the data regis-

ter), DRDY does not reset high. DRDY remains low until

the new data is read from the data register or until

FSYNC goes low to begin a new conversion.

Table 15 provides the duration-to-mode bits and dura-

tion-to-DRDY for each calibration sequence. Duration-to-

mode bits provide the time required for the calibration

sequence to complete (MD1 and MD0 return to 0).

Duration-to-DRDY provides the time until the first conver-

sion result is valid in the data register (DRDY goes low).

The pipeline delay necessary to ensure that the first

conversion result is valid is tP (tP = 2000 x 1/fCLKIN).

When selecting self-calibration (MD1 = 0, MD0 = 1),

DRDY goes low 9 x 1/output data rate + tP after FSYNC

goes low (or after a write operation to the setup register

with MD1 = 0 and MD0 = 1 is performed while FSYNC

is already low) to indicate new data in the data register.

The pipeline delay required to ensure that the first con-

version result is valid is tP (tP = 2000 x 1/fCLKIN).

When zero-scale or full-scale calibration is selected,

DRDY goes low 4 x 1/output data rate + tP after FSYNC

goes low (or while the zero-scale or full-scale calibra-

tion command is issued when FSYNC is already low) to

indicate new data in the data register (see the

Calibration section).

Calibration

To compensate for errors introduced by temperature

variations or system DC offsets, perform an on-chip cal-

ibration. Select calibration options by writing to the

MD1 and MD0 bits in the setup register (Table 9).

Calibration removes gain and offset errors from the

device and/or the system. Recalibrate with changes in

ambient temperature, supply voltage, bipolar/unipolar

mode, PGA gain, and output data rate.

The MX7705 offers two calibration modes, self-calibra-

tion and system calibration. The channels of the

MX7705 are independently calibrated (Table 8). The

calibration coefficients resulting from a calibration

sequence on a selected channel are stored in the corre-

sponding offset and gain-register pair.

Self- and system calibration automatically calculate the

offset and gain coefficients, which are written to the off-

set and gain registers. These offset and gain coeffi-

cients provide offset and gain-error correction for the

specified channel.

Self-Calibration

Self-calibration compensates for offset and gain errors

internal to the ADC. Prior to calibration, set the PGA gain,

unipolar/bipolar mode, and input channel setting. During

self-calibration, AIN+ and AIN- of the selected channel

are internally shorted together. The ADC calibrates this

condition as the zero-scale output level. For bipolar

mode, this zero-scale point is the midscale of the bipolar

transfer function.

16-Bit, Low-Power, 2-Channel,

Sigma-Delta ADC

28

______________________________________________________________________________________

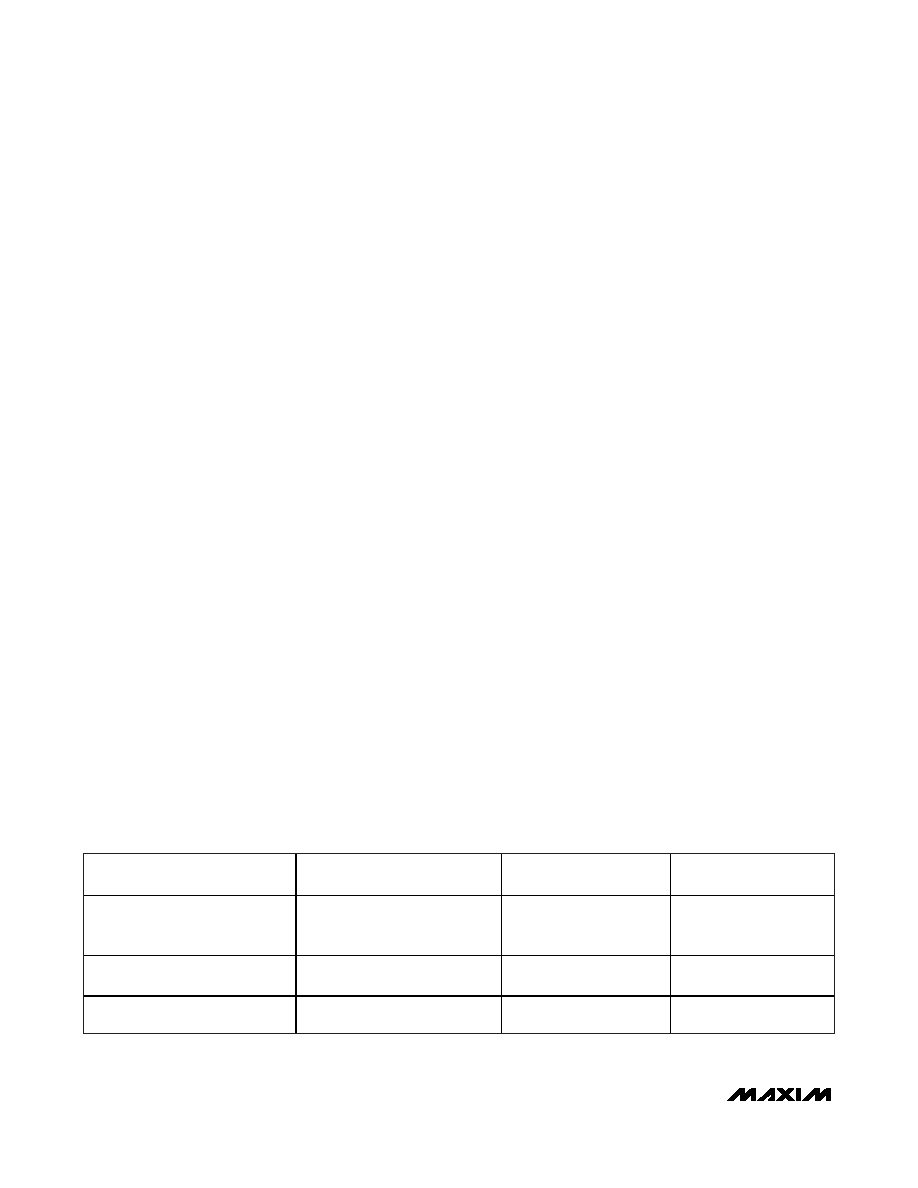

Table 15. Calibration Sequences

CALIBRATION TYPE

(MD1, MD0)

CALIBRATION SEQUENCE

DURATION-TO-MODE

BITS*

DURATION TO

DRDY**

Self-calibration (0,1)

Internal zero-scale calibration at

selected gain + internal full-scale

calibration at selected gain

6 x 1/output data rate

9 x 1/output data rate + tP

Zero-scale system calibration (1,0)

Zero-scale calibration on AIN at

selected gain

3 x 1/output data rate

4 x 1/output data rate + tP

Full-scale system calibration (1,1)

Full-scale calibration on AIN at

selected gain

3 x 1/output data rate

4 x 1/output data rate + tP

*

Duration-to-mode bits represents the completion of the calibration sequence.

**

Duration to DRDY represents the time at which a new conversion result is available in the data register.

相关PDF资料 |

PDF描述 |

|---|---|

| MS3102E20-29S | CONN RCPT 17POS BOX MNT W/SCKT |

| VE-22Y-MV | CONVERTER MOD DC/DC 3.3V 99W |

| MS3100A18-11P | CONN RCPT 5POS WALL MNT W/PINS |

| MAX165BCWN+ | IC ADC CMOS 8BIT UP COMP 18SOIC |

| VE-20H-MX | CONVERTER MOD DC/DC 52V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MX7705EPE+ | 功能描述:模数转换器 - ADC 16-Bit 2Ch Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MX7705EUE | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MX7705EUE+ | 功能描述:模数转换器 - ADC 16-Bit 2Ch Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MX7705EUE+T | 功能描述:模数转换器 - ADC 16-Bit 2Ch Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MX7705EUE-T | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。