- 您现在的位置:买卖IC网 > PDF目录378681 > N74F574D (NXP Semiconductors N.V.) Octal transparent latch (3-State); Octal transparent latch (3-State) PDF资料下载

参数资料

| 型号: | N74F574D |

| 厂商: | NXP Semiconductors N.V. |

| 元件分类: | 通用总线功能 |

| 英文描述: | Octal transparent latch (3-State); Octal transparent latch (3-State) |

| 封装: | N74F573D<SOT163-1 (SO20)|<<http://www.nxp.com/packages/SOT163-1.html<1<week 4, 2004,;N74F573D<SOT163-1 (SO20)|<<http://www.nxp.com/packages/SOT163-1.html<1<week 4, |

| 文件页数: | 2/14页 |

| 文件大小: | 118K |

| 代理商: | N74F574D |

Philips Semiconductors

Product specification

74F573/74F574

Latch/flip-flop

74F573 Octal Transparent Latch (3-State)

74F574 Octal D Flip-Flop (3-State)

2

1989 Oct 16

853-0083 97897

FEATURES

74F573 is broadside pinout version of 74F373

74F574 is broadside pinout version of 74F374

Inputs and Outputs on opposite side of package allow easy

interface to Microprocessors

Useful as an Input or Output port for Microprocessors

3-State Outputs for Bus interfacing

Common Output Enable

74F563 and 74F564 are inverting version of 74F573 and 74F574

respectively

3-State Outputs glitch free during power-up and power-down

These are High-Speed replacements for N8TS805 and N8TS806

DESCRIPTION

The 74F573 is an octal transparent latch coupled to eight 3-State

output buffers. The two sections of the device are controlled

independently by Enable (E) and Output Enable (OE) control gates.

The 74F573 is functionally identical to the 74F373 but has a

broadside pinout configuration to facilitate PC board layout and

allow easy interface with microprocessors.

The data on the D inputs is transferred to the latch outputs when the

Enable (E) input is High. The latch remains transparent to the data

input while E is High and stores the data that is present one setup

time before the High-to-Low enable transition.

The 3-State output buffers are designed to drive heavily loaded

3-State buses, MOS memories, or MOS microprocessors. The

active Low Output Enable (OE) controls all eight 3-State buffers

independent to the latch operation. When OE is Low, the latched or

transparent data appears at the outputs. When OE is High, the

outputs are in high impedance “off” state, which means they will

neither drive nor load the bus.

The 74F574 is functionally identical to the 74F374 but has a

broadside pinout configuration to facilitate PC board layout and

allow easy interface with microprocesors.

It is an 8-bit, edge triggered register coupled to eight 3-State output

buffers. The two sections of the device are controlled independently

by the clock (CP) and Output Enable (OE) control gates.

The register is fully edge-triggered. The state of each D input, one

setup time before the Low-to-High clock transition is transferred to

the corresponding flip-flop’s Q output.

The 3-State output buffers are designed to drive heavily loaded

3-State buses, MOS memories, or MOS microprocessors. The

active Low Output Enable (OE) controls all eight 3-State buffers

independently of the latch operation. When OE is Low, the latched

or transparent data appears at the outputs. When OE is High, the

outputs are in high impedance “off” state, which means they will

neither drive nor load the bus.

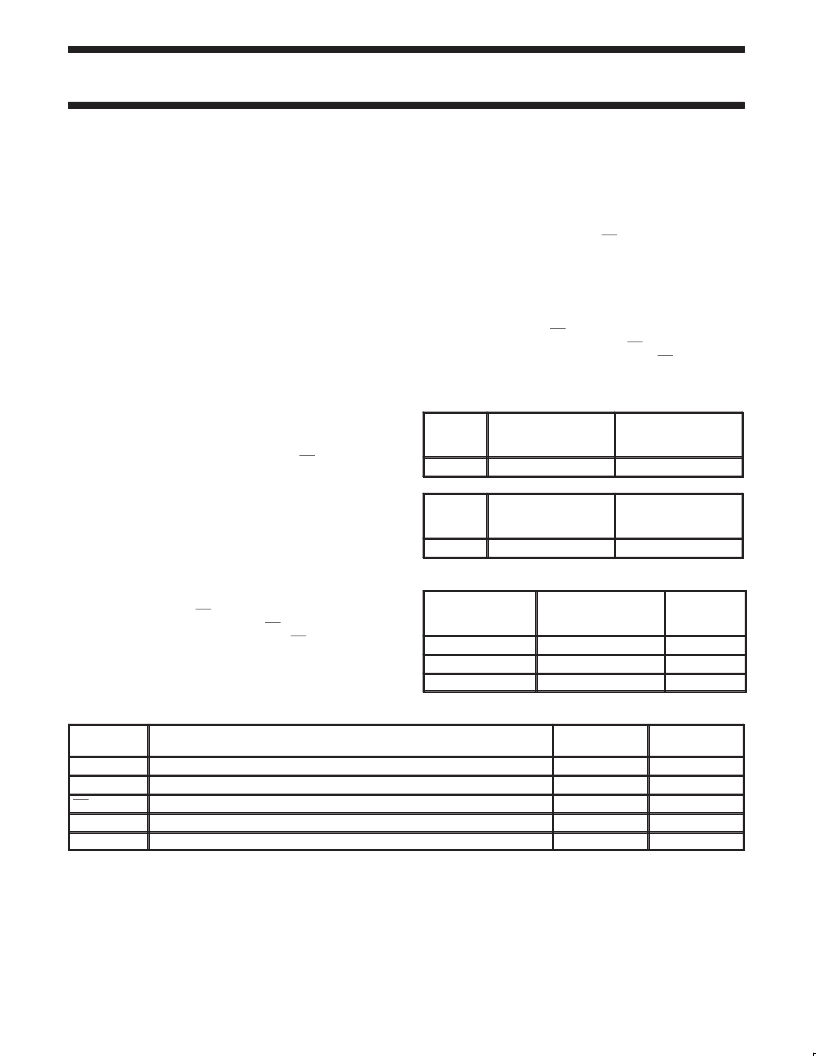

TYPE

TYPICAL

PROPAGATION DELAY

TYPICAL SUPPLY

CURRENT

(TOTAL)

74F573

5.0ns

35mA

TYPE

TYPICAL f

MAX

TYPICAL SUPPLY

CURRENT

(TOTAL)

74F574

180MHz

50mA

ORDERING INFORMATION

DESCRIPTION

COMMERCIAL RANGE

V

CC

= 5V

±

10%,

T

amb

= 0

°

C to +70

°

C

PKG DWG #

20-Pin Plastic DIP

N74F573N, N74F574N

SOT146-1

20-Pin Plastic SOL

N74F573D, N74F574D

SOT163-1

20-Pin Plastic SSOP

N74F573DB

SOT339-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS

DESCRIPTION

74F (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

D0 - D7

Data inputs

1.0/1.0

20

μ

A/0.6mA

20

μ

A/0.6mA

20

μ

A/0.6mA

20

μ

A/0.6mA

E (74F573)

Latch Enable input (active falling edge)

1.0/1.0

OE

Output Enable input (active Low)

1.0/1.0

CP (74F574)

Clock Pulse input (active rising edge)

1.0/1.0

Q0 - Q7

NOTE:

One (1.0) FAST Unit Load is defined as: 20

μ

A in the High state and 0.6mA in the Low state.

3-State outputs

150/40

3.0mA/24mA

相关PDF资料 |

PDF描述 |

|---|---|

| N74F574N | Octal transparent latch (3-State); Octal transparent latch (3-State) |

| NE57814DD | DDR memory termination regulator with standby mode and enhanced efficiency |

| NVT2008BQ | Bidirectional voltage-level translator for open-drain and push-pull applications |

| NVT2008PW | Bidirectional voltage-level translator for open-drain and push-pull applications |

| NVT2010BQ | Bidirectional voltage-level translator for open-drain and push-pull applications |

相关代理商/技术参数 |

参数描述 |

|---|---|

| N74F574D,602 | 功能描述:触发器 OCTAL D FLIP-FLOP RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

| N74F574D,623 | 功能描述:触发器 OCTAL D FLIP-FLOP RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

| N74F574D+623 | 制造商:NXP Semiconductors 功能描述:Flip Flop D-Type Bus Interface Pos-Edge 3-ST 1-Element 20-Pin SO T/R 制造商:NXP Semiconductors 功能描述:Cut Tape |

| N74F574DB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Octal D-Type Flip-Flop |

| N74F574D-T | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Octal D-Type Flip-Flop |

发布紧急采购,3分钟左右您将得到回复。