- 您现在的位置:买卖IC网 > PDF目录299557 > NJU3716AVC2 SERIAL IN PARALLEL OUT SHIFT REGISTER, PDSO24 PDF资料下载

参数资料

| 型号: | NJU3716AVC2 |

| 元件分类: | 计数移位寄存器 |

| 英文描述: | SERIAL IN PARALLEL OUT SHIFT REGISTER, PDSO24 |

| 封装: | SSOP-24 |

| 文件页数: | 3/8页 |

| 文件大小: | 60K |

| 代理商: | NJU3716AVC2 |

NJU3555

NJU3555

NJU3716A

-3 -

Ver.2008-07-18

FUNCTIONAL DESCRIPTION

(1) Reset

When the "L" level is input to the CLR terminal, all latches are reset and all of parallel conversion

output are "L" level.

Normally, the CLR terminal should be "H" level.

(2) Data Transmission

In the STB terminal is "H" level and the clock signals are inputted to the CLK terminal, the serial data

into the DATA terminal are shifted in the shift register synchronizing at a rising edge of the clock signal.

When the STB terminal is changed to "L" level, the data in the shift register are transferred to the

latches.

Even if the STB terminal is "L" level, the input clock signal shifts the data in the shift register, therefore,

the clock signal should be controlled for data order.

(3) Cascade Connection

The serial data input from DATA terminal is output from the SO terminal through internal shift register

unrelated with the CLR and STB status.

Furthermore, the 4 input circuits provide a hysteresis characteristics using the schmitt trigger structure

to protect the noise.

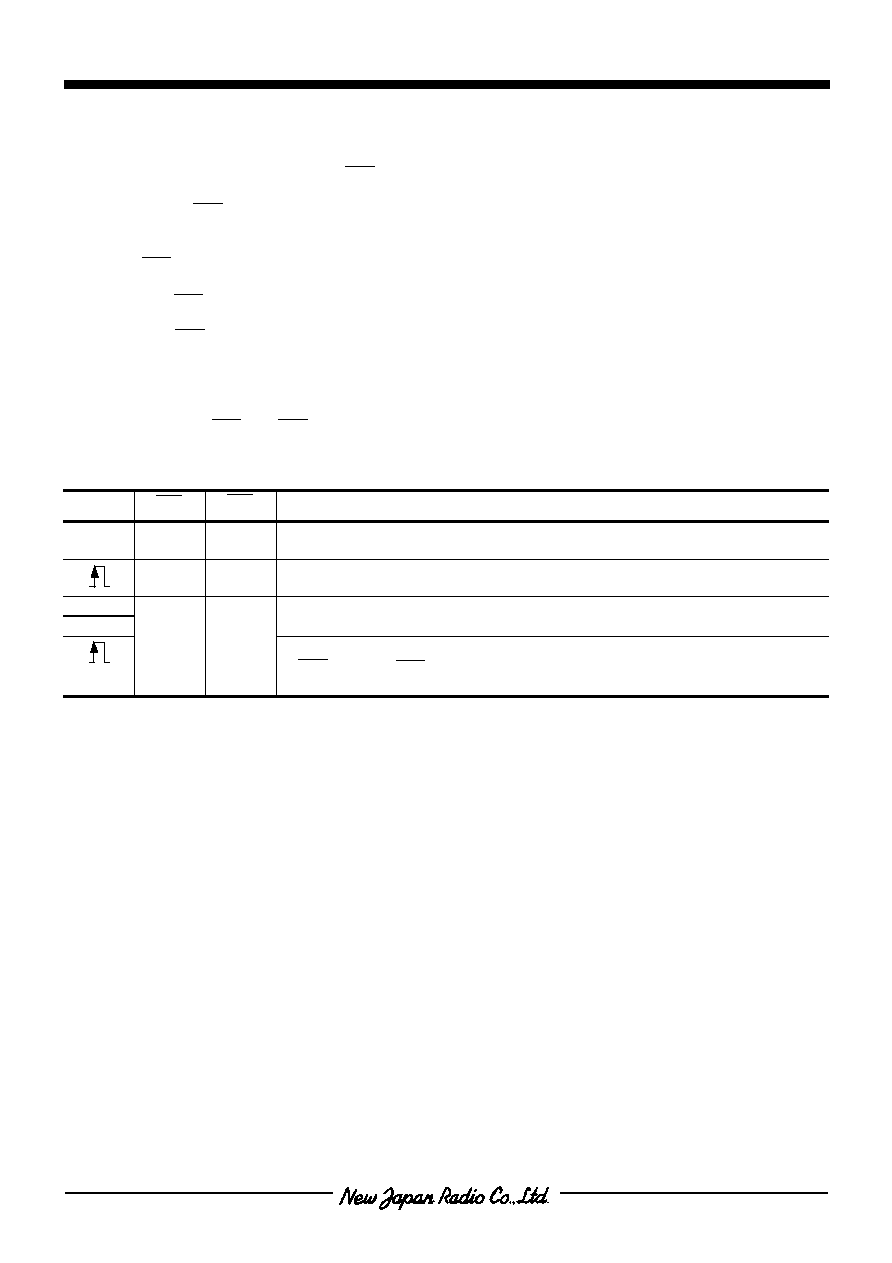

CLK

STB

CLR

OPERATION

X

L

All of latches are reset (the data in the shift register is no change).

All of parallel conversion outputs are "L".

H

The serial data into the DATA terminal are inputted to the shift register.

In this stage, the data in the latch is not changed.

L

H

The data in the shift register is transferred to the latch. And the data in the

latch is output from the parallel conversion output terminals.

L

H

When the clock signal is inputted into the CLK terminal in state of the

STB="L" and CLR="H", the data is shifted in the shift register and latched

data is also changed in accordance with the shift register.

Note 1) X: Don’t care

相关PDF资料 |

PDF描述 |

|---|---|

| NJU7283CM(TE3) | BATTERY CHARGE CONTROLLER, PDSO8 |

| NJU7773F05 | 5 V FIXED POSITIVE LDO REGULATOR, 0.22 V DROPOUT, PDSO5 |

| NJU7773F21 | 2.1 V FIXED POSITIVE LDO REGULATOR, 0.3 V DROPOUT, PDSO5 |

| NJU7773F27 | 2.7 V FIXED POSITIVE LDO REGULATOR, 0.28 V DROPOUT, PDSO5 |

| NJU7773F22 | 2.2 V FIXED POSITIVE LDO REGULATOR, 0.3 V DROPOUT, PDSO5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| NJU3716AVC2-TE1 | 制造商:New Japan Radio Co Ltd (NJR/JRC) 功能描述:16-BIT SERIAL TO PARALLEL CONVERTER WITH SSOP24-C2 PKG 制造商:New Japan Radio Co Ltd (NJR/JRC) 功能描述:Serial Parallel Converter 16-Bit SSOP24 |

| NJU3716L | 功能描述:串行到并行逻辑转换器 16bit Srial to Prll RoHS:否 制造商:Supertex 工作电源电压: 安装风格:SMD/SMT 封装 / 箱体:QFN-32 封装:Tray |

| NJU3716M | 功能描述:计数器移位寄存器 16bit Srial to Prll RoHS:否 制造商:Texas Instruments 计数器类型: 计数顺序:Serial to Serial/Parallel 电路数量:1 封装 / 箱体:SOIC-20 Wide 逻辑系列: 逻辑类型: 输入线路数量:1 输出类型:Open Drain 传播延迟时间:650 ns 最大工作温度:+ 125 C 最小工作温度:- 40 C 封装:Reel |

| NJU3716M-T2 | 功能描述:计数器移位寄存器 16bit Srial to Prll RoHS:否 制造商:Texas Instruments 计数器类型: 计数顺序:Serial to Serial/Parallel 电路数量:1 封装 / 箱体:SOIC-20 Wide 逻辑系列: 逻辑类型: 输入线路数量:1 输出类型:Open Drain 传播延迟时间:650 ns 最大工作温度:+ 125 C 最小工作温度:- 40 C 封装:Reel |

| NJU3716M-TE1 | 功能描述:计数器移位寄存器 16-Bit Serial to Parallel Convertr RoHS:否 制造商:Texas Instruments 计数器类型: 计数顺序:Serial to Serial/Parallel 电路数量:1 封装 / 箱体:SOIC-20 Wide 逻辑系列: 逻辑类型: 输入线路数量:1 输出类型:Open Drain 传播延迟时间:650 ns 最大工作温度:+ 125 C 最小工作温度:- 40 C 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。