- 您现在的位置:买卖IC网 > PDF目录367727 > P87C770AAR (NXP SEMICONDUCTORS) Microcontrollers for NTSC TVs with On-Screen Display OSD and Closed Caption CC PDF资料下载

参数资料

| 型号: | P87C770AAR |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | Microcontrollers for NTSC TVs with On-Screen Display OSD and Closed Caption CC |

| 中文描述: | 8-BIT, OTPROM, 12 MHz, MICROCONTROLLER, PDIP52 |

| 文件页数: | 51/80页 |

| 文件大小: | 266K |

| 代理商: | P87C770AAR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

1999 Jun 11

51

Philips Semiconductors

Product specification

Microcontrollers for NTSC TVs with On-Screen

Display (OSD) and Closed Caption (CC)

P8xCx70 family

18.8

General controls

18.8.1

P

OLARITY OF

HSYNC

AND

VSYNC

INPUT SIGNALS

The horizontal and vertical input sync signals can be

inverted by setting the HPOL and VPOL bits in the Text

Vertical Position Register (see Section 18.9.2).

Table 74

Sync signal polarity

18.8.2

F

RAME RESET GENERATION

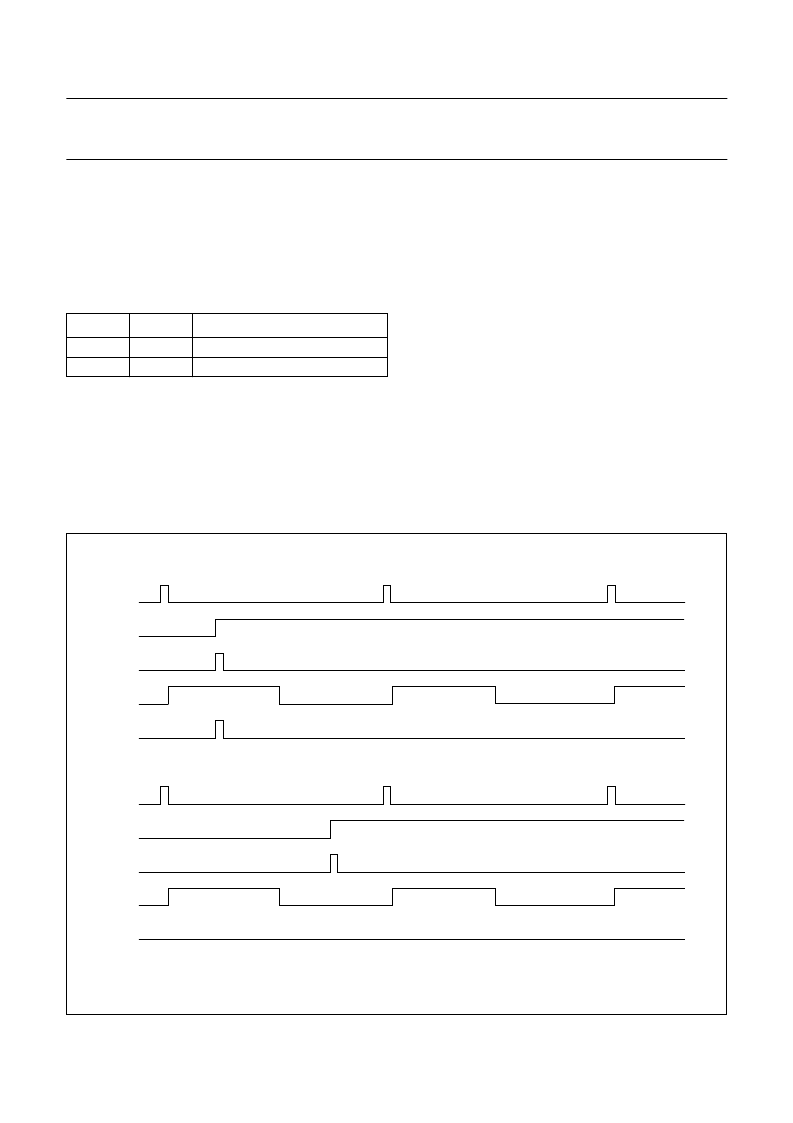

Normally, VSYNC of the first field occurs during the first

half line period and Vsync of the second field occurs during

the second half period of a scan-line. In this case it is very

easy to generate a frame reset signal. The VSYNC pulse

is generated by sampling and rising edge detection.

HPOL

VPOL

SYNC SIGNAL POLARITY

0

1

0

1

input polarity

input inverted polarity

These VSYNC pulses are gated (AND gate) with a line

frequency signal which has a duty cycle of 50 : 50 (H50).

The output signal is the frame reset pulse. The rising edge

of the H50 signal is generated from the HSYNC pulse.

The falling edge is generated via a comparison between

the fixed value of half of the nominal number of 768 pixels

per line (comparator value: 384 pixels) and the value of a

pixel counter.

If the VSYNC of one field occurs shortly after the falling

edge of H50 and the line period has more than the nominal

number of 768 pixels per line, it is possible that both

VSYNC pulses occur during the low period of H50.

The result is that no frame reset pulse is generated. In the

case of a VSYNC pulse occurring shortly after the rising

edge of H50 and less than the nominal number of

768 pixels per line it is possible that every VSYNC pulse

will generate a frame reset pulse. To prevent this

happening the position of H50 is adjustable in increments

of 12 clock cycles. The adjustment value is selected using

the Odd/Even Align Register.

Fig.22 Frame reset timing.

handbook, full pagewidth

MGL151

Hsync

Frame

reset

H50

Vsync_In

Vsync

(sampled)

Hsync

Frame

reset

Field 2

H50

Vsync_In

Vsync

(sampled)

相关PDF资料 |

PDF描述 |

|---|---|

| P83C270 | Microcontrollers for NTSC TVs with On-Screen Display (OSD) and Closed Caption (CC)(在NTSC TV中应用的具有屏幕显示和字幕关闭特点的微控制器) |

| P83C370 | Microcontrollers for NTSC TVs with On-Screen Display (OSD) and Closed Caption (CC)(在NTSC TV中应用的具有屏幕显示和字幕关闭特点的微控制器) |

| P87C770 | Microcontrollers for NTSC TVs with On-Screen Display (OSD) and Closed Caption (CC)(在NTSC TV中应用的具有屏幕显示和字幕关闭特点的微控制器) |

| P83C270AAR | Microcontrollers for NTSC TVs with On-Screen Display OSD and Closed Caption CC |

| P83C434CFP | ECONOLINE: RU - Twin Independent Outputs- Output/Output Isolation 1kVDC- Power Sharing on Outputs- Input/Output Isolation 1kVDC- No Heatsink Required- UL94V-0 Package Material- Toroidal Magnetics- No Extern. Components Required- Custom Solutions Available- Efficiency t |

相关代理商/技术参数 |

参数描述 |

|---|---|

| P87L42 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:UNIVERSAL PERIPHERAL INTERFACE CHMOS 8-BIT SLAVE MICROCONTROLLER |

| P87LPC759 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Low power, low price, low pin count (14 pin) microcontroller with 1 kbyte OTP |

| P87LPC759BN | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Low power, low price, low pin count (14 pin) microcontroller with 1 kbyte OTP |

| P87LPC760 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Low power, low price, low pin count (14 pin) microcontroller with 1 kbyte OTP |

| P87LPC760BDH | 功能描述:8位微控制器 -MCU 80C51 1K/128 OTP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。