- 您现在的位置:买卖IC网 > PDF目录367742 > P89C662HBA (NXP SEMICONDUCTORS) 80C51 8-bit Flash microcontroller family PDF资料下载

参数资料

| 型号: | P89C662HBA |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 80C51 8-bit Flash microcontroller family |

| 中文描述: | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PQCC44 |

| 封装: | PLASTIC, MS-018, SOT-187-2, LCC-44 |

| 文件页数: | 16/89页 |

| 文件大小: | 491K |

| 代理商: | P89C662HBA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

Philips Semiconductors

Product data

P89C660/P89C662/P89C664/

P89C668

80C51 8-bit Flash microcontroller family

16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

2002 Oct 28

16

Serial Clock Generator

This programmable clock pulse generator provides the SCL clock

pulses when SIO1 is in the Master Transmitter or Master Receiver

mode. It is switched off when SIO1 is in a Slave mode. The

programmable output clock frequencies are: f

OSC

/120, f

OSC

/9600

(12-clock mode) or f

OSC

/60, f

OSC

/4800 (6-clock mode) and the

Timer 1 overflow rate divided by eight. The output clock pulses have

a 50% duty cycle unless the clock generator is synchronized with

other SCL clock sources as described above.

Timing and Control

The timing and control logic generates the timing and control signals

for serial byte handling. This logic block provides the shift pulses for

S1DAT, enables the comparator, generates and detects start and

stop conditions, receives and transmits acknowledge bits, controls

the master and Slave modes, contains interrupt request logic, and

monitors the I

2

C bus status.

Control Register, S1CON

This 7-bit special function register is used by the microcontroller to

control the following SIO1 functions: start and restart of a serial

transfer, termination of a serial transfer, bit rate, address recognition,

and acknowledgment.

Status Decoder and Status Register

The status decoder takes all of the internal status bits and

compresses them into a 5-bit code. This code is unique for each I

2

C

bus status. The 5-bit code may be used to generate vector

addresses for fast processing of the various service routines. Each

service routine processes a particular bus status. There are 26

possible bus states if all four modes of SIO1 are used. The 5-bit

status code is latched into the five most significant bits of the status

register when the serial interrupt flag is set (by hardware) and

remains stable until the interrupt flag is cleared by software. The

three least significant bits of the status register are always zero. If

the status code is used as a vector to service routines, then the

routines are displaced by eight address locations. Eight bytes of

code is sufficient for most of the service routines.

The Four SIO1 Special Function Registers

The microcontroller interfaces to SIO1 via four special function

registers. These four SFRs (S1ADR, S1DAT, S1CON, and S1STA)

are described individually in the following sections.

The Address Register, S1ADR

The CPU can read from and write to this 8-bit, directly addressable

SFR. S1ADR is not affected by the SIO1 hardware. The contents of

this register are irrelevant when SIO1 is in a Master mode. In the

Slave modes, the seven most significant bits must be loaded with

the microcontroller’s own slave address, and, if the least significant

bit is set, the general call address (00H) is recognized; otherwise it

is ignored.

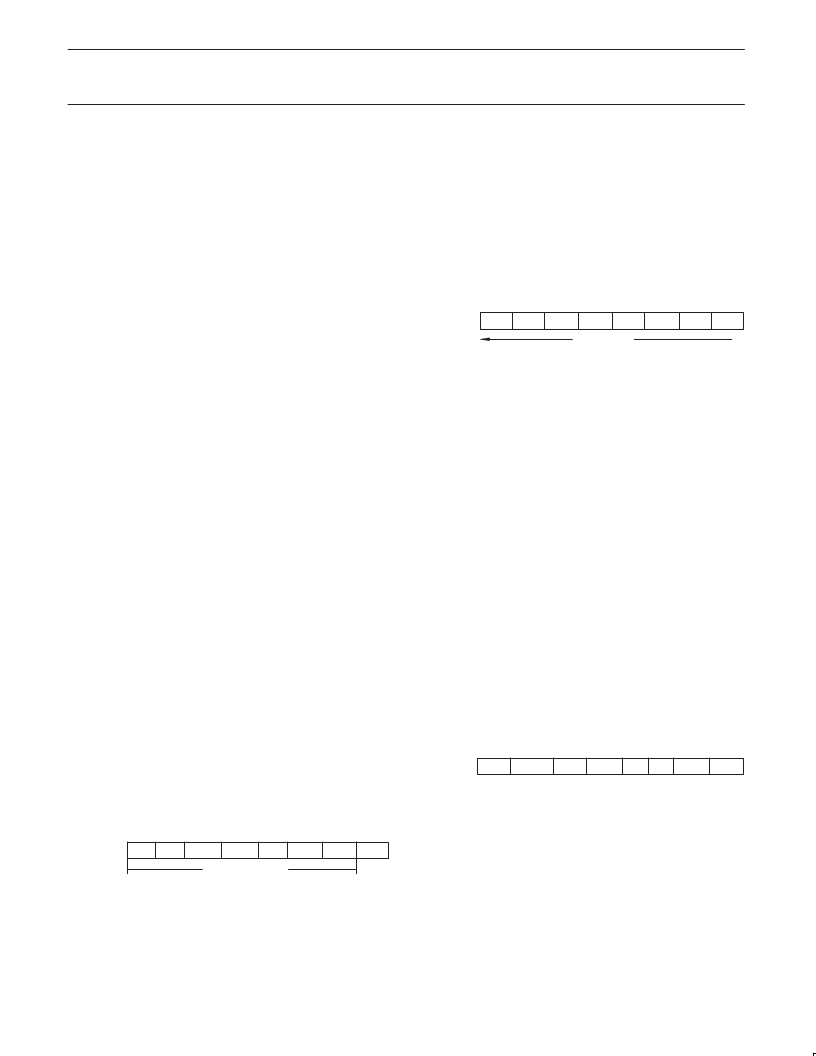

S1ADR (DBH)

X

GC

7

6

5

4

3

2

1

0

own slave address

X

X

X

X

X

X

The most significant bit corresponds to the first bit received from the

I

2

C bus after a start condition. A logic 1 in S1ADR corresponds to a

high level on the I

2

C bus, and a logic 0 corresponds to a low level

on the bus.

The Data Register, S1DAT

S1DAT contains a byte of serial data to be transmitted or a byte

which has just been received. The CPU can read from and write to

this 8-bit, directly addressable SFR while it is not in the process of

shifting a byte. This occurs when SIO1 is in a defined state and the

serial interrupt flag is set. Data in S1DAT remains stable as long as

SI is set. Data in S1DAT is always shifted from right to left: the first

bit to be transmitted is the MSB (bit 7), and, after a byte has been

received, the first bit of received data is located at the MSB of

S1DAT. While data is being shifted out, data on the bus is

simultaneously being shifted in; S1DAT always contains the last

data byte present on the bus. Thus, in the event of lost arbitration,

the transition from master transmitter to slave receiver is made with

the correct data in S1DAT.

S1DAT (DAH)

SD7

SD6

SD5

SD4

SD3

SD2

SD1

SD0

7

6

5

4

3

2

1

0

shift direction

SD7 - SD0:

Eight bits to be transmitted or just received. A logic 1 in S1DAT

corresponds to a high level on the I

2

C bus, and a logic 0

corresponds to a low level on the bus. Serial data shifts through

S1DAT from right to left. Figure 6 shows how data in S1DAT is

serially transferred to and from the SDA line.

S1DAT and the ACK flag form a 9-bit shift register which shifts in or

shifts out an 8-bit byte, followed by an acknowledge bit. The ACK

flag is controlled by the SIO1 hardware and cannot be accessed by

the CPU. Serial data is shifted through the ACK flag into S1DAT on

the rising edges of serial clock pulses on the SCL line. When a byte

has been shifted into S1DAT, the serial data is available in S1DAT,

and the acknowledge bit is returned by the control logic during the

ninth clock pulse. Serial data is shifted out from S1DAT via a buffer

(BSD7) on the falling edges of clock pulses on the SCL line.

When the CPU writes to S1DAT, BSD7 is loaded with the content of

S1DAT.7, which is the first bit to be transmitted to the SDA line (see

Figure 7). After nine serial clock pulses, the eight bits in S1DAT will

have been transmitted to the SDA line, and the acknowledge bit will

be present in ACK. Note that the eight transmitted bits are shifted

back into S1DAT.

The Control Register, S1CON

The CPU can read from and write to this 8-bit, directly addressable

SFR. Two bits are affected by the SIO1 hardware: the SI bit is set

when a serial interrupt is requested, and the STO bit is cleared when

a STOP condition is present on the I

2

C bus. The STO bit is also

cleared when ENS1 = “0”.

S1CON (D8H)

ENS1

STA

STO

SI

AA

CR1

CR0

7

6

5

4

3

2

1

0

CR2

ENS1, the SIO1 Enable Bit:

ENS1 = “0”: When ENS1 is “0”, the

SDA and SCL outputs are in a high impedance state. SDA and SCL

input signals are ignored, SIO1 is in the “not addressed” slave state,

and the STO bit in S1CON is forced to “0”. No other bits are

affected. P1.6 and P1.7 may be used as open drain I/O ports.

ENS1 = “1”: When ENS1 is “1”, SIO1 is enabled. The P1.6 and P1.7

port latches must be set to logic 1.

ENS1 should not be used to temporarily release SIO1 from the I2C

bus since, when ENS1 is reset, the I2C bus status is lost. The AA

flag should be used instead (see description of the AA flag in the

following text).

相关PDF资料 |

PDF描述 |

|---|---|

| P89C662HBBD | 80C51 8-bit Flash microcontroller family |

| P89C664HBA | 80C51 8-bit Flash microcontroller family |

| P89C664HBBD | 80C51 8-bit Flash microcontroller family |

| P89C662 | 80C51 8-Bit Flash Microcontroller 32KB ISP/IAP FLASH with 1KB RAM(80C51 8位闪速微控制器,带16KB ISP/IAP闪速存储器和1KB RAM) |

| P89C668HBA | 80C51 8-bit Flash microcontroller family 64KB ISP FLASH with 8KB RAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| P89C662HBA/00,512 | 功能描述:IC 80C51 MCU FLASH 32K 44-PLCC RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:89C 产品培训模块:MCU Product Line Introduction XMEGA Introduction AVR XMEGA USB Connectivity 标准包装:90 系列:AVR® XMEGA 核心处理器:AVR 芯体尺寸:8/16-位 速度:32MHz 连通性:I²C,IrDA,SPI,UART/USART 外围设备:欠压检测/复位,DMA,POR,PWM,WDT 输入/输出数:50 程序存储器容量:192KB(96K x 16) 程序存储器类型:闪存 EEPROM 大小:4K x 8 RAM 容量:16K x 8 电压 - 电源 (Vcc/Vdd):1.6 V ~ 3.6 V 数据转换器:A/D 16x12b; D/A 2x12b 振荡器型:内部 工作温度:-40°C ~ 85°C 封装/外壳:64-TQFP 包装:托盘 配用:ATSTK600-RC14-ND - STK600 SOCKET/ADAPTER 64TQFPATSTK600-TQFP64-ND - STK600 SOCKET/ADAPTER 64-TQFPATAVRONEKIT-ND - KIT AVR/AVR32 DEBUGGER/PROGRMMRATAVRISP2-ND - PROGRAMMER AVR IN SYSTEM |

| P89C662HBBD | 制造商: 功能描述: 制造商:undefined 功能描述: |

| P89C662HBBD/00,557 | 制造商:NXP Semiconductors 功能描述: |

| P89C662HFA | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:80C51 8-bit Flash microcontroller family |

| P89C662HFA/00,512 | 功能描述:8位微控制器 -MCU 32K/1K FL 6 CLK ISP/IAP IND RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。