- 您现在的位置:买卖IC网 > PDF目录224672 > PALCE22V10H-10PI/5 (LATTICE SEMICONDUCTOR CORP) 24-Pin EE CMOS (Zero Power) Versatile PAL Device PDF资料下载

参数资料

| 型号: | PALCE22V10H-10PI/5 |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | 24-Pin EE CMOS (Zero Power) Versatile PAL Device |

| 中文描述: | EE PLD, 10 ns, PDIP24 |

| 封装: | 0.300 INCH, SKINNY, PLASTIC, DIP-24 |

| 文件页数: | 23/34页 |

| 文件大小: | 691K |

| 代理商: | PALCE22V10H-10PI/5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

PALCE22V10 and PALCE22V10Z Families

3

Variable Input/Output Pin Ratio

The PALCE22V10 has twelve dedicated input lines, and each macrocell output can be an I/O pin.

Buffers for device inputs have complementary outputs to provide user-programmable input signal

polarity. Unused input pins should be tied to VCC or GND.

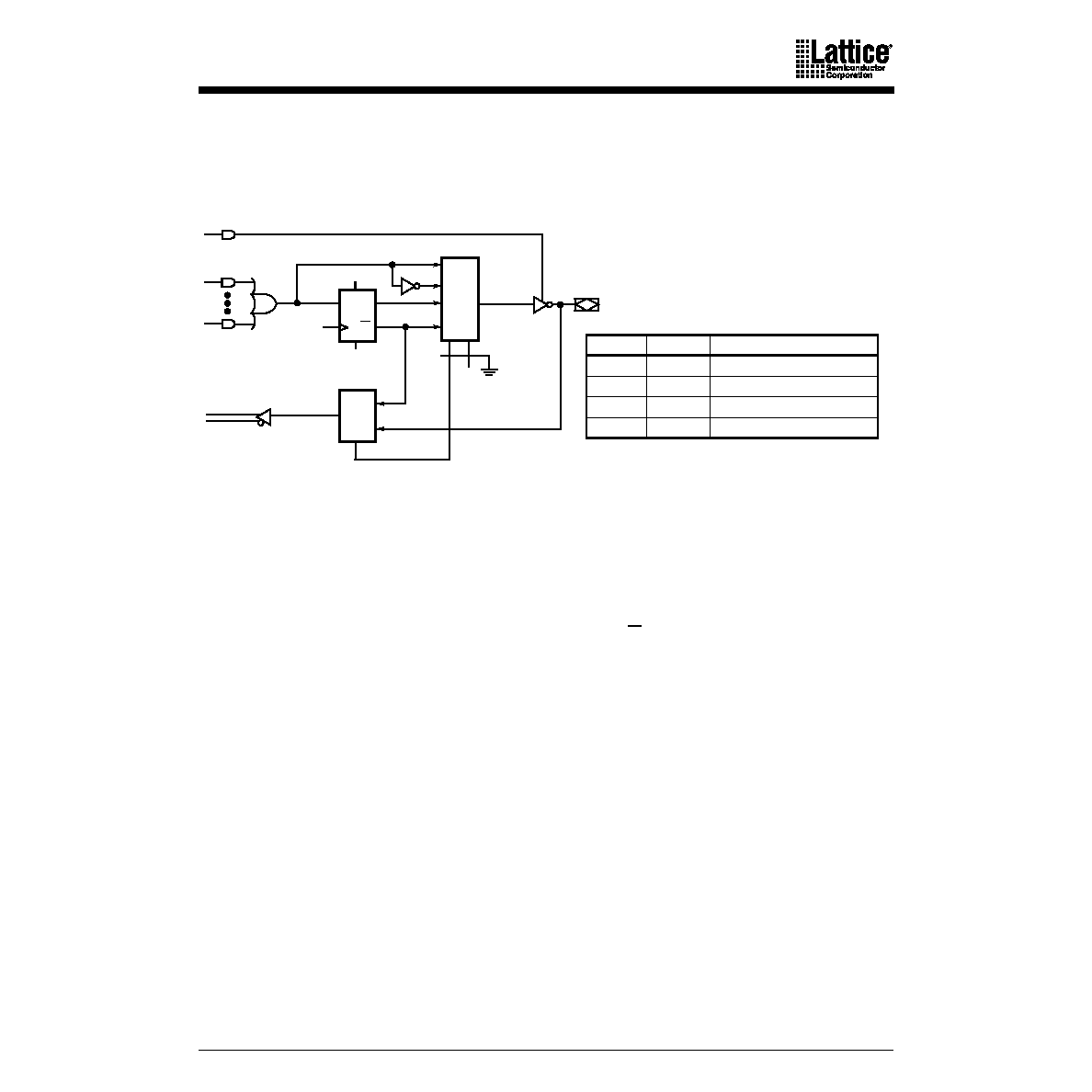

Registered Output Conguration

Each macrocell of the PALCE22V10 includes a D-type ip-op for data storage and

synchronization. The ip-op is loaded on the LOW-to-HIGH transition of the clock input. In the

registered conguration (S1 = 0), the array feedback is from Q of the ip-op.

Combinatorial I/O Conguration

Any macrocell can be congured as combinatorial by selecting the multiplexer path that bypasses

the ip-op (S1 = 1). In the combinatorial conguration, the feedback is from the pin.

0 = Programmed EE bit

1 = Erased (charged) EE bit

Figure 1. Output Logic Macrocell Diagram

16564E-004

CLK

S1

10

11

00

01

AR

SP

0

1

I/On

S0

D Q

Q

S1

S0

Output Conguration

0

Registered/Active Low

0

1

Registered/Active High

1

0

Combinatorial/Active Low

1

Combinatorial/Active High

相关PDF资料 |

PDF描述 |

|---|---|

| PALCE22V10H-10SC/5 | 24-Pin EE CMOS (Zero Power) Versatile PAL Device |

| PALCE22V10Q-10JC/5 | 24-Pin EE CMOS (Zero Power) Versatile PAL Device |

| PALCE22V10Q-10PC/5 | 24-Pin EE CMOS (Zero Power) Versatile PAL Device |

| PALCE22V10Q-15JC/5 | 24-Pin EE CMOS (Zero Power) Versatile PAL Device |

| PALCE22V10Q-15PC/5 | 24-Pin EE CMOS (Zero Power) Versatile PAL Device |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PALCE22V10H-10SC/5 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:24-Pin EE CMOS (Zero Power) Versatile PAL Device |

| PALCE22V10H10ZC/5 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:ASIC |

| PALCE22V10H-15/B3A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Electrically-Erasable PLD |

| PALCE22V10H-15/BKA | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Electrically-Erasable PLD |

| PALCE22V10H-15/BLA | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Electrically-Erasable PLD |

发布紧急采购,3分钟左右您将得到回复。