- 您现在的位置:买卖IC网 > PDF目录296795 > PCA84C122BT (NXP SEMICONDUCTORS) 8-bit microcontrollers for remote control transmitters PDF资料下载

参数资料

| 型号: | PCA84C122BT |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-bit microcontrollers for remote control transmitters |

| 中文描述: | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PDSO20 |

| 封装: | 7.50 MM, PLASTIC, SOT-163-1, SO-20 |

| 文件页数: | 24/24页 |

| 文件大小: | 142K |

| 代理商: | PCA84C122BT |

1995 May 01

9

Philips Semiconductors

Product specication

8-bit microcontrollers for

remote control transmitters

PCA84C122; 222; 422; 622; 822

8.1.1

ON-TIME REGISTER (ADDRESS: 00H)

This 8-bit register is loaded by software; the decimal value

of its contents + 2, determine the number of oscillator

cycles that the OUT pin is active.

The active period (ON-time) of OUT

8.1.2

OFF-TIME REGISTER (ADDRESS: 01H)

This 8-bit register is loaded by software; the decimal value

of its contents + 2, determine the number of oscillator

cycles that the OUT pin is inactive.

The inactive period (OFF-time) of OUT

contents

2

+

()

f

osc

---------------------------------------

=

contents

2

+

()

f

osc

---------------------------------------

=

8.1.3

PULSE COUNTER

The Pulse Counter, is a 10-bit register consisting of:

Pulse Counter Low (8-bit); address 02H.

Pulse Counter High (2-bit); address 04H.

The Pulse Counter is loaded by software with the number

of pulses required in a pulse burst; loading ‘0’ is not

allowed.

8.1.4

CONTROL REGISTER (ADDRESS 03H)

The Control Register contains the bits that control various

possibilities for the output pulses, plus the reset of the

interrupt flip-flop and the Watchdog timer.

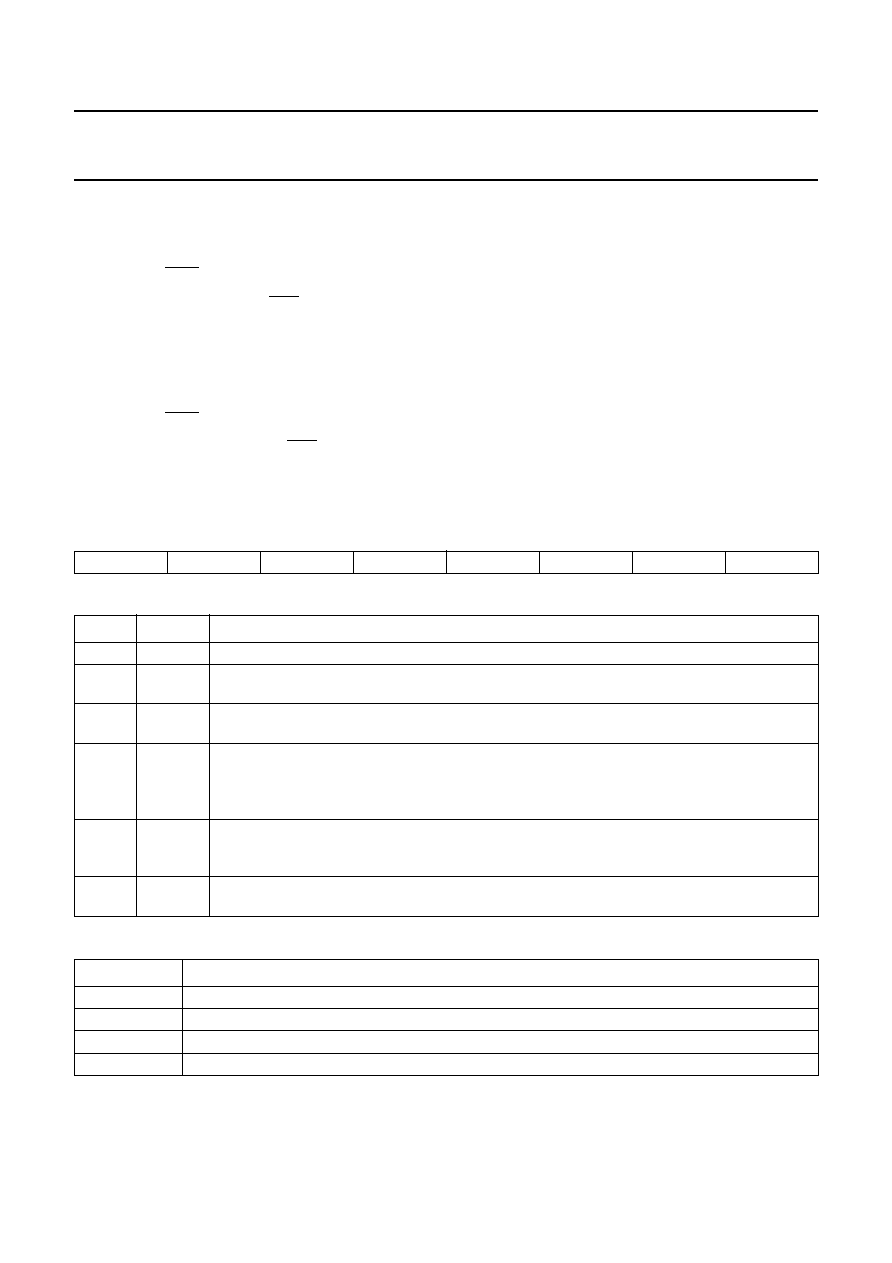

Table 2

Control Register (CR)

Table 3

Description of the CR bits

8.2

Instructions for data transfer between the 84CXXX core and derivative logic

76543210

RWDT

Rint

PWM

LgP

HF

BIT

SYMBOL

DESCRIPTION

7to5

Reserved.

4

RWDT

Reload Watchdog Timer: This is not an actual ip-op in the Control Register. If a logic 1 is

written to this bit position the Watchdog Timer is reloaded (reset to 0); this bit is Write only.

3

Rint

Reset Interrupt: This is not an actual ip-op in the Control Register. If a logic 1 is written to this

bit position the interrupt ip-op is reset; this bit is Write only.

2

PWM

Pulse Width Modulation: Is the standard term for a quasi analog signal. It is a square wave

signal of which the duty cycle may be varied. When integrated a real analog signal may be

obtained. When PWM = 1; the Pulse Counter Register is ignored and a continuous pulse train is

generated (see Fig.9); this bit is Read or Write.

1

LgP

Long Pulse: When LgP = 1; the OFF-time Register is ignored and a single pulse of length

is generated. If HF = 1, this pulse is modulated with a

frequency 1

4 × fosc (see Fig.10); this bit is Read or Write.

0HF

High Frequency: When HF = 1 the ON-time part of the generated pulse is modulated with a

frequency 1

4 × fosc (see Fig.11); this bit is Read or Write.

INSTRUCTION

DESCRIPTION

MOV Dx,A

Move contents of the accumulator to the derivative register.

MOV A,Dx

Move contents of derivative register to the accumulator.

ANL Dx,A

AND derivative register contents with contents of accumulator. Result is stored in derivative register.

ORL Dx,A

OR derivative register contents with contents of accumulator. Result is stored in derivative register.

ON-time

()

number of pulses

()

×

=

相关PDF资料 |

PDF描述 |

|---|---|

| PCA873/CG/HPAS | SPECIALTY TELECOM CIRCUIT, PQCC28 |

| PCA9510D,118 | SPECIALTY INTERFACE CIRCUIT, PDSO8 |

| PCA9549BS | Octal bus switch with individually I2C-bus controlled enables |

| PCA9549D | Octal bus switch with individually I2C-bus controlled enables |

| PCA9549PW | Octal bus switch with individually I2C-bus controlled enables |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PCA84C222 | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:8-bit microcontrollers for remote control transmitters |

| PCA84C222A | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:8-bit microcontrollers for remote control transmitters |

| PCA84C222AP | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:8-bit microcontrollers for remote control transmitters |

| PCA84C222AT | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:8-bit microcontrollers for remote control transmitters |

| PCA84C222B | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:8-bit microcontrollers for remote control transmitters |

发布紧急采购,3分钟左右您将得到回复。