- 您现在的位置:买卖IC网 > PDF目录69043 > PE3336-52 (PEREGRINE SEMICONDUCTOR CORP) PHASE LOCKED LOOP, 3000 MHz, QCC44 PDF资料下载

参数资料

| 型号: | PE3336-52 |

| 厂商: | PEREGRINE SEMICONDUCTOR CORP |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PHASE LOCKED LOOP, 3000 MHz, QCC44 |

| 封装: | 7 X 7 MM, GREEN, QFN-44 |

| 文件页数: | 16/16页 |

| 文件大小: | 359K |

| 代理商: | PE3336-52 |

Product Specification

PE3336

Document No. 70-0033-04

│ www.psemi.com

Page 9 of 16

2005-2010 Peregrine Semiconductor Corp. All rights reserved.

input is “low”, serial input data (Sdata input), B0 to

B7, are clocked serially into the enhancement

register on the rising edge of Sclk, MSB (B0) first.

The enhancement register is double buffered to

prevent inadvertent control changes during serial

loading, with buffer capture of the serially entered

data performed on the falling edge of E_WR

according to the timing diagram shown in Figure

5. After the falling edge of E_WR, the data provide

control bits as shown in Table 8 with bit

functionality enabled by asserting the Enh input

“low”.

Direct Interface Mode

Direct Interface Mode is selected by setting the

Bmode

input “high”.

Counter control bits are set directly at the pins as

shown in Table 7. In Direct Interface Mode, main

counter inputs M7 and M8, and R Counter inputs

R4 and R5 are internally forced low (“0”).

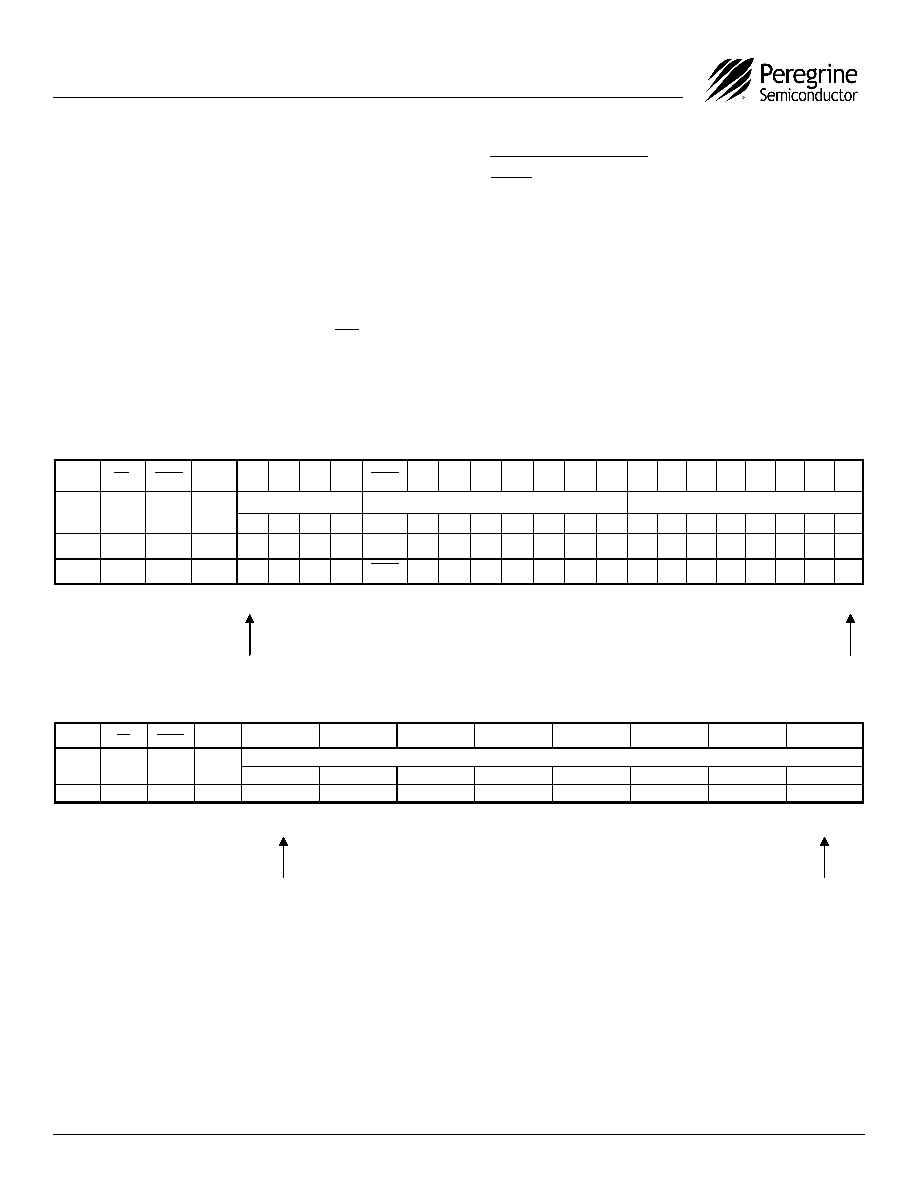

MSB (first in)

(last in) LSB

Interface

Mode

Enh

Bmode

Smode

R5

R4

M8

M7

Pre_en

M6

M5

M4

M3

M2

M1

M0

R3

R2

R1

R0

A3

A2

A1

A0

Parallel

1

0

M2_WR rising edge load

M1_WR rising edge load

A_WR rising edge load

D3

D2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

Serial*

1

0

1

B0

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

Direct

1

X

0

Pre_en

M6

M5

M4

M3

M2

M1

M0

R3

R2

R1

R0

A3

A2

A1

A0

Table 7. Primary Register Programming

Table 8. Enhancement Register Programming

*Serial data clocked serially on Sclk rising edge while E_WR “low” and captured in secondary register on S_WR rising edge.

Interface

Mode

Enh

Bmode

Smode

Reserved

Power

down

Counter

load

MSEL

output

Prescaler

output

fc, fp OE

Parallel

0

X

0

E_WR rising edge load

D7

D6

D5

D4

D3

D2

D1

D0

Serial*

0

X

1

B0

B1

B2

B3

B4

B5

B6

B7

*Serial data clocked serially on Sclk rising edge while E_WR “high” and captured in the double buffer on E_WR falling edge.

MSB (first in)

(last in) LSB

相关PDF资料 |

PDF描述 |

|---|---|

| PE3336-53 | PHASE LOCKED LOOP, 3000 MHz, PQCC44 |

| PE3336-21 | PHASE LOCKED LOOP, 3000 MHz, PQCC44 |

| PE3336-00 | PHASE LOCKED LOOP, 3000 MHz, QCC44 |

| PE3336-22 | PHASE LOCKED LOOP, 3000 MHz, PQCC44 |

| PE3339-12 | PHASE LOCKED LOOP, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PE3336EK | 制造商:PEREGRINE 制造商全称:PEREGRINE 功能描述:3000 MHz UltraCMOS⑩ Integer-N PLL for Low Phase Noise Applications |

| PE33370LF | 制造商:PASTERNACK 制造商全称:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG217/U HN MALE TO HN MALE(LEAD FREE) |

| PE33383 | 制造商:PASTERNACK 制造商全称:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG316/U BNC MALE TO TNC MALE |

| PE3339 | 制造商:PEREGRINE 制造商全称:PEREGRINE 功能描述:3.0 GHz Integer-N PLL for Low Phase Noise Applications |

| PE33399 | 制造商:PASTERNACK 制造商全称:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG11A/U 75 OHM BNC MALE TO 75 OHM BNC MALE |

发布紧急采购,3分钟左右您将得到回复。