- 您现在的位置:买卖IC网 > PDF目录369994 > PEX8648-AARDK (PLX Technology, Inc.) PCIe Gen2, 5.0GT/s 48-lane, 12-port PCIe Switch PDF资料下载

参数资料

| 型号: | PEX8648-AARDK |

| 厂商: | PLX Technology, Inc. |

| 英文描述: | PCIe Gen2, 5.0GT/s 48-lane, 12-port PCIe Switch |

| 中文描述: | 的PCIe Gen2,5.0GT / s的48通道,12端口PCIe交换器 |

| 文件页数: | 2/4页 |

| 文件大小: | 237K |

| 代理商: | PEX8648-AARDK |

Preliminary - PLX Confidential

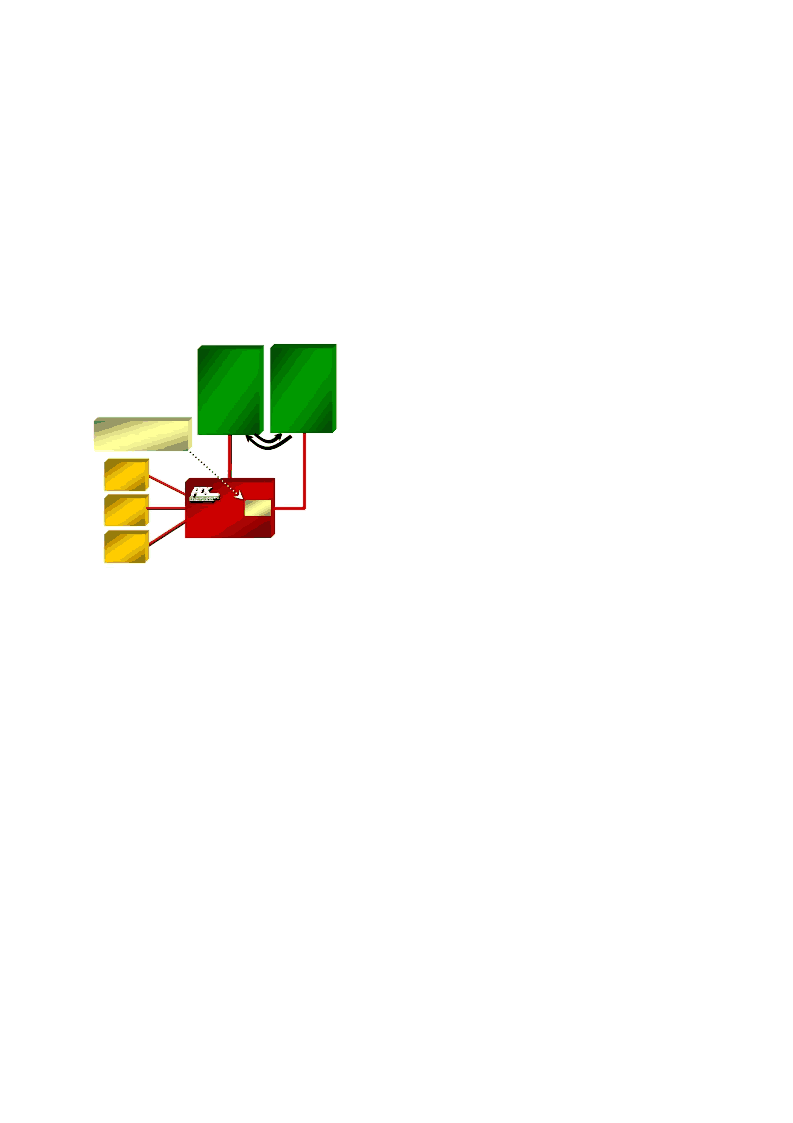

Dual-Host & Failover Support

The PEX 8648 product supports a

Non-Transparent

(NT) Port,

which enables the implementation of

multi-

host systems

in communications, storage, and blade

server applications. The NT port allows systems to

isolate host memory domains by presenting the

processor subsystem as an endpoint rather than another

memory system. Base address registers are used to

translate addresses; doorbell registers are used to send

interrupts between the address domains; and scratchpad

registers (accessible by both CPUs) allow inter-

processor communication (see Figure 2).

I/O

Figure 2. Non-Transparent Port

Dual Cast

The PEX 8648 supports Dual Cast, a feature which

allows for the copying of data (e.g. packets) from one

ingress port to two egress ports allowing for higher

performance in dual-graphics, storage, security, and

redundant applications.

Read Pacing

The Read Pacing feature allows users to throttle the

amount of read requests being made by downstream

devices. When a downstream device requests several

long reads back-to-back, the Root Complex gets tied up

in serving this downstream port. If this port has a narrow

link and is therefore slow in receiving these read packets

from the Root Complex, then other downstream ports

may become starved – thus, impacting performance. The

Read Pacing feature enhances performances by allowing

for the adequate servicing of all downstream devices.

Hot Plug for High Availability

Hot plug capability allows users to replace hardware

modules and perform maintenance without powering

down the system. The PEX 8648 hot plug capability

feature makes it suitable for

High Availability (HA)

applications

. Three downstream ports include a

Standard Hot Plug Controller. If the PEX 8648 is used in

I/O

I/O

Blade

CPU

Host

Primary

Non-Transparent

Port

PEX 8648

NT

Blade

CPU

Host

Secondary

an application where one or more of its downstream

ports connect to PCI Express slots, each port’s Hot Plug

Controller can be used to manage the hot-plug event of

its associated slot. Every port on the PEX 8648 is

equipped with a hot-plug control/status register to

support hot-plug capability through external logic via the

I

2

C interface.

SerDes Power and Signal Management

The PEX 8648 supports software control of the SerDes

outputs to allow optimization of power and signal

strength in a system. The PLX SerDes implementation

supports four levels of power – off, low, typical, and

high. The SerDes block also supports

loop-back modes

and

advanced reporting of error conditions

, which

enables efficient management of the entire system.

Interoperability

The PEX 8648 is designed to be fully compliant with the

PCI Express Base Specification r2.0, and is backwards

compatible to PCI Express Base Specification r1.1 and

r1.0a. Additionally, it supports

auto-negotiation

,

lane

reversal

, and

polarity reversal

. Furthermore, the PEX

8648 is tested for Microsoft Vista compliance. All PLX

switches undergo thorough interoperability testing in

PLX’s

Interoperability Lab

and

compliance testing at

the PCI-SIG plug-fest.

Applications

Suitable for

host-centric

as well as

peer-to-peer traffic

patterns,

the PEX 8648 can be configured for a wide

variety of form factors and applications.

Host Centric Fan-out

The PEX 8648, with its symmetric or asymmetric lane

configuration capability, allows user-specific tuning to a

variety of host-centric applications. Figure 3 shows a

typical

server

design where the root complex provides a

PCI Express link that needs to be expanded to a larger

number of smaller ports for a variety of I/O functions. In

this example, the PEX 8648 has a 16-lane upstream port,

and five downstream ports using x8 and x4 links.

The PEX 8648 can also be used to create PCIe Gen1 (2.5

Gbps) ports. The PEX 8648 is backwards compatible

with PCIe Gen1 devices. Therefore, the PEX 8648

enables a Gen 2 native Chip Set to fan-out to Gen 1

endpoints. In Figure 3, the PCIe slots connected to the

PEX 8648’s downstream ports can be populated with

either PCIe Gen1 or PCIe Gen 2 devices. Conversely,

the PEX 8648 can also be used to create Gen 2 ports on

a Gen 1 native Chip Set in the same fashion.

相关PDF资料 |

PDF描述 |

|---|---|

| PF0348 | 4.5A, 500kHz Step-Down Switching Regulator; Package: SO; No of Pins: 8; Temperature Range: -40°C to +85°C |

| PF0349 | 4.5A, 500kHz Step-Down Switching Regulator; Package: SO; No of Pins: 8; Temperature Range: -40°C to +85°C |

| PF0350 | 4.5A, 500kHz Step-Down Switching Regulator; Package: SO; No of Pins: 8; Temperature Range: -40°C to +85°C |

| PF0351 | 500kHz and 1MHz High Efficiency 1.5A Switching Regulators; Package: SO; No of Pins: 8; Temperature Range: -40?°C to 85?°C |

| PF0352 | 500kHz and 1MHz High Efficiency 1.5A Switching Regulators; Package: SO; No of Pins: 8; Temperature Range: -40?°C to 85?°C |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PEX8648-BB50B8F | 功能描述:外围驱动器与原件 - PCI 48 Lane, 12 Port PCI Express Gen 2 Switch RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| PEX8648-BB50BIF | 功能描述:外围驱动器与原件 - PCI 48 Lane 12 Port PCIe Switch RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| PEX8648-BB50RBC F | 功能描述:PCI Express? Switch IC 676-FCBGA (27x27) 制造商:broadcom limited 系列:ExpressLane? 包装:托盘 零件状态:在售 应用:PCI Express? 多路复用器/解复用器电路:- 开关电路:- 通道数:- 导通电阻(最大值):- 电压 -?电源,单(V+):- 电压 - 电源,双(V±):- -3db 带宽:- 特性:可配置 工作温度:- 封装/外壳:- 供应商器件封装:676-FCBGA(27x27) 标准包装:200 |

| PEX8649 | 制造商:PLX 制造商全称:PLX 功能描述:PCI Express Gen 2 Switch, 48 Lanes, 12 Ports |

| PEX8649-16U16DAICRDK | 制造商:PLX 制造商全称:PLX 功能描述:PCI Express Gen 2 Switch, 48 Lanes, 12 Ports |

发布紧急采购,3分钟左右您将得到回复。