- 您现在的位置:买卖IC网 > PDF目录365365 > PI90LV03 (Pericom Semiconductor Corp.) SOTiny LVDS Repeater PDF资料下载

参数资料

| 型号: | PI90LV03 |

| 厂商: | Pericom Semiconductor Corp. |

| 英文描述: | SOTiny LVDS Repeater |

| 中文描述: | SOTiny的LVDS中继器 |

| 文件页数: | 1/7页 |

| 文件大小: | 337K |

| 代理商: | PI90LV03 |

1

PS8660A 07/07/04

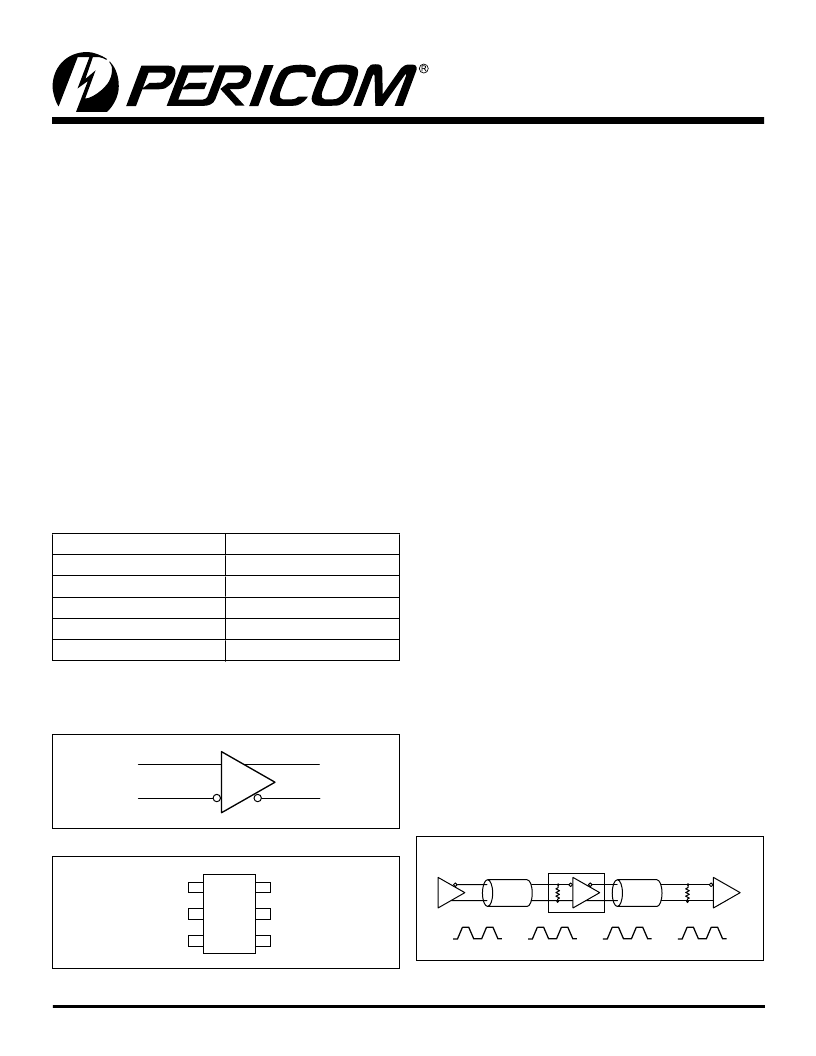

Pin Configuration

Features

Complies with ANSI/TIA/EIA-644-A LVDS standard

LVDS receiver inputs accept LVPECL signals

Low jitter 660 Mbps fully differential data path

Bus-Terminal ESD exceeds 2kV

Single +3.3V supply voltage operation

Receiver Differential Input Voltage Threshold < ±100mV

Receiver open-circuit failsafe

Low-Voltage Differential Signaling with typical Output Volt-

ages of 350mV into:

– 100 Load (PI90LV03)

– 50 Load (PI90LVB03)

Typical Propagation Delay Times of 1.5ns

Typical Power Dissipation of 20mW @ 200 MHz

Outputs are High Impedance with V

CC

< 1.5V

Industrial Temperature Range: –40°C to 85°C

Packaging:

- 6-pin space-saving SOT-23 (T)

PI90LV03/PI90LVB03

Function Table

Inputs

Outputs

V

Y

- V

Z

H

X

L

H

V

ID

= V

A

- V

B

V

ID

> 50mV

50mV < V

ID

< 50mV

V

ID

≤ -50mV

Open

Description

PI90LV03 and PI90LVB03 are single LVDS Repeaters that use

low-voltage differential signaling (LVDS) to support data rates up

to 660 Mbps. The PI90LVB03 features high-drive output. Both

products are designed for applications requiring high-speed, low-

power consumption, low-noise generation, and a small package.

The LVDS Repeaters take an LVDS input signal and provide an

LVDS output to address various interface logic requirements such

as signal isolation, repeater, stub length, and Optical Transceiver

Modules. In many large systems, signals are distributed across

backplanes, and the distance between the transmission line and the

unterminated receivers are one of the limiting factors for system

speed. The buffers can be used to reduce the ‘stub length’ by stra-

tegic device placement along the trace length. They can improve

system performance by allowing the receiver to be placed very

close to the main transmission line or very close to the connector

on the card. Longer traces to the LVDS receiver can then be placed

after the buffer.

The buffer’s wide input dynamic range enables them to receive dif-

ferential signals from LVPECL and LVDS sources. The devices can

be used as compact high-speed serial translators between LVPECL

and LVDS data lines. The differential translation provides a simple

way to mix and match Optical Transceiver ICs from various vendors

without redesigning the interfaces.

Applications

The PI90LV03 and PI90LVB03 provide differential translation

between LVDS and PECL devices for high-speed, point-to-point

interface and telecom applications:

– ATM

– SONET/SDH

– Switches

– Routers

– Add-Drop Multiplexers

Block Diagram

Notes:

1.

H = high level; L = low level; X = indeterminate

SOTiny

LVDS Repeater

High-Speed Differential Cable Repeater Application

1

2

3

V

DD

GND

A

B

Y

Z

6

5

4

5

4

Y

Z

1

A

2

B

Z

O

RT = Z

O

TX

Any LVDS R

X

R

T

= ZO

LVDS Repeater

Z

O

相关PDF资料 |

PDF描述 |

|---|---|

| PI90LV03TX | SOTiny LVDS Repeater |

| PI90LVB03 | SOTiny LVDS Repeater |

| PI90LVB03TEX | SOTiny LVDS Repeater |

| PI90LVB03TX | SOTiny LVDS Repeater |

| PI90LV03TEX | SOTiny LVDS Repeater |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PI90LV031A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LVDS | Quad LVDS Driver (EN) |

| PI90LV031AL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Line Driver |

| PI90LV031ALE | 功能描述:缓冲器和线路驱动器 LVDS Driver (EN) Quad RoHS:否 制造商:Micrel 输入线路数量:1 输出线路数量:2 极性:Non-Inverting 电源电压-最大:+/- 5.5 V 电源电压-最小:+/- 2.37 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:MSOP-8 封装:Reel |

| PI90LV031ALEX | 功能描述:总线发射器 Quad LVDS Line Drivr RoHS:否 制造商:Texas Instruments 数据速率:135 Mpps 接口: 电源电压-最大:3.6 V 电源电压-最小:3 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:TSSOP-56 封装:Reel |

| PI90LV031AW | 功能描述:IC QUAD LVDS LINE DRIVER 16-SOIC RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,000 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-SOIC(0.295",7.50mm 宽) 供应商设备封装:16-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。