- 您现在的位置:买卖IC网 > PDF目录10906 > PIC12C672T-10I/SM (Microchip Technology)IC MCU OTP 2KX14 A/D 8-SOIJ PDF资料下载

参数资料

| 型号: | PIC12C672T-10I/SM |

| 厂商: | Microchip Technology |

| 文件页数: | 2/129页 |

| 文件大小: | 0K |

| 描述: | IC MCU OTP 2KX14 A/D 8-SOIJ |

| 标准包装: | 2,100 |

| 系列: | PIC® 12C |

| 核心处理器: | PIC |

| 芯体尺寸: | 8-位 |

| 速度: | 10MHz |

| 外围设备: | POR,WDT |

| 输入/输出数: | 5 |

| 程序存储器容量: | 3.5KB(2K x 14) |

| 程序存储器类型: | OTP |

| RAM 容量: | 128 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 3 V ~ 5.5 V |

| 数据转换器: | A/D 4x8b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.209",5.30mm 宽) |

| 包装: | 带卷 (TR) |

| 配用: | XLT08SO-1-ND - SOCKET TRANSITION 8SOIC 150/208 AC164312-ND - MODULE SKT FOR PM3 16SOIC 309-1048-ND - ADAPTER 8-SOIC TO 8-DIP 309-1047-ND - ADAPTER 8-SOIC TO 8-DIP |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页

PIC12C67X

DS30561B-page 10

1999 Microchip Technology Inc.

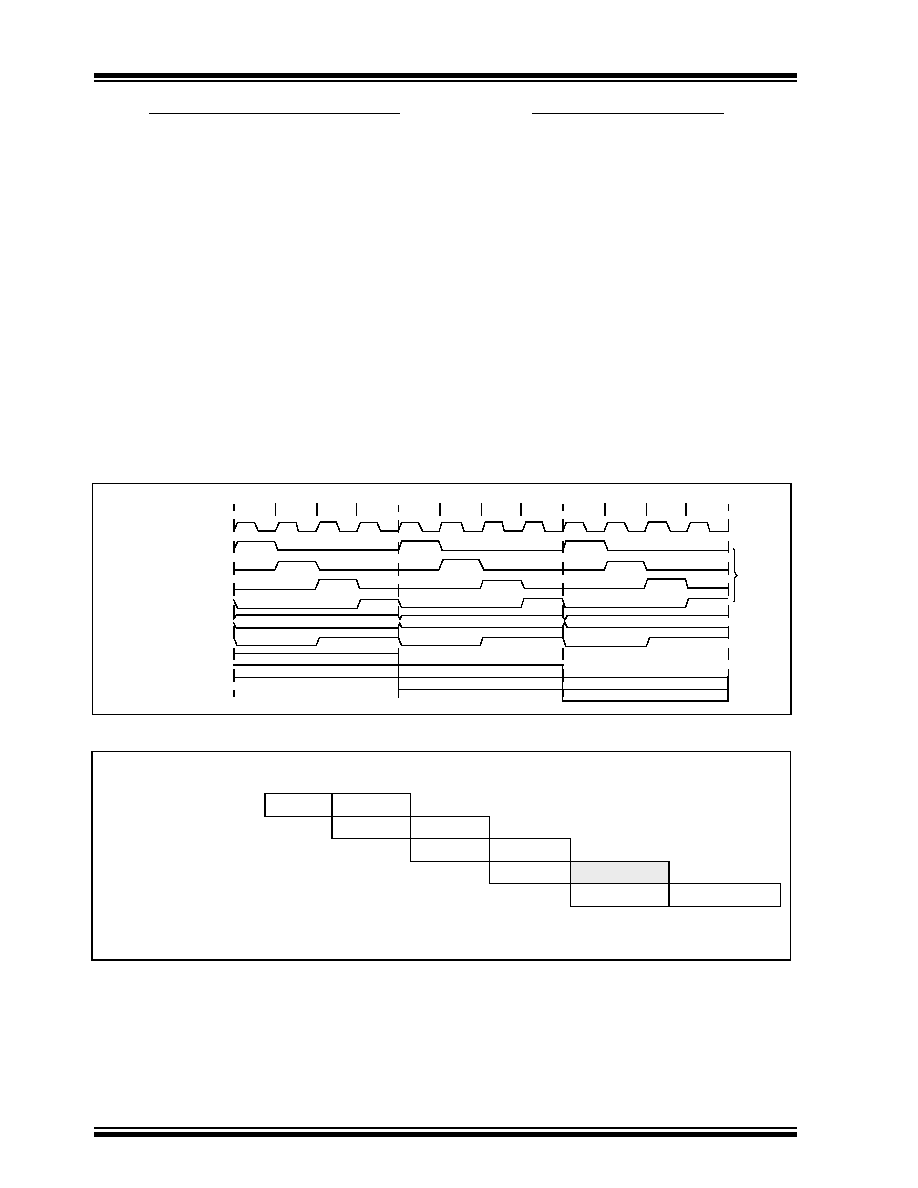

FIGURE 3-2:

CLOCK/INSTRUCTION CYCLE

EXAMPLE 3-1:

INSTRUCTION PIPELINE FLOW

Q1

Q2

Q3

Q4

Q1

Q2

Q3

Q4

Q1

Q2

Q3

Q4

OSC1

Q1

Q2

Q3

Q4

PC

OSC2/CLKOUT

(EXTRC and

PC

PC+1

PC+2

Fetch INST (PC)

Execute INST (PC-1)

Fetch INST (PC+1)

Execute INST (PC)

Fetch INST (PC+2)

Execute INST (PC+1)

Internal

phase

clock

INTRC modes)

All instructions are single cycle, except for any program branches. These take two cycles since the fetched

instruction is “flushed” from the pipeline while the new instruction is being fetched and then executed.

TCY0TCY1TCY2TCY3TCY4TCY5

1. MOVLW 55h

Fetch 1

Execute 1

2. MOVWF GPIO

Fetch 2

Execute 2

3. CALL

SUB_1

Fetch 3

Execute 3

4. BSF

GPIO, BIT3 (Forced NOP)

Fetch 4

Flush

5. Instruction @ address SUB_1

Fetch SUB_1

Execute SUB_1

3.1

Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by

four to generate four non-overlapping quadrature

clocks, namely Q1, Q2, Q3 and Q4. Internally, the pro-

gram counter (PC) is incremented every Q1, and the

instruction is fetched from the program memory and

latched into the instruction register in Q4. The instruc-

tion is decoded and executed during the following Q1

through Q4. The clocks and instruction execution flow

is shown in Figure 3-2.

3.2

Instruction Flow/Pipelining

An “Instruction Cycle” consists of four Q cycles (Q1,

Q2, Q3 and Q4). The instruction fetch and execute

are pipelined such that fetch takes one instruction

cycle, while decode and execute takes another

instruction cycle. However, due to the pipelining, each

instruction effectively executes in one cycle. If an

instruction causes the program counter to change

(i.e., GOTO), then two cycles are required to complete

the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC)

incrementing in Q1.

In the execution cycle, the fetched instruction is

latched into the “Instruction Register" (IR) in cycle

Q1. This instruction is then decoded and executed

during the Q2, Q3, and Q4 cycles. Data memory is

read during Q2 (operand read) and written during Q4

(destination write).

相关PDF资料 |

PDF描述 |

|---|---|

| MT2492SMI-92-SP | MODEM V.92 SERIAL DATA 5V |

| VI-J6V-IY-B1 | CONVERTER MOD DC/DC 5.8V 50W |

| MT2492SMI-92 | MODEM V.92 SERIAL DATA 5V |

| PIC12C672T-10E/SM | IC MCU OTP 2KX14 A/D 8-SOIJ |

| MT2492SMI-L-34-SP | MODEM V.34 SERIAL DATA 3.3V |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PIC12C67X | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:8-Pin, 8-Bit CMOS Microcontroller with A/D Converter and EEPROM Data Memory |

| PIC12C67X_13 | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:8-Pin, 8-Bit CMOS Microcontroller with A/D Converter and EEPROM Data Memory |

| PIC12CE-04/EJW | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:8-Pin, 8-Bit CMOS Microcontrollers |

| PIC12CE-04/EP | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:8-Pin, 8-Bit CMOS Microcontrollers |

| PIC12CE-04/ESM | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:8-Pin, 8-Bit CMOS Microcontrollers |

发布紧急采购,3分钟左右您将得到回复。