- 您现在的位置:买卖IC网 > PDF目录10887 > PIC16C63AT-04E/SS (Microchip Technology)IC MCU OTP 4KX14 PWM 28SSOP PDF资料下载

参数资料

| 型号: | PIC16C63AT-04E/SS |

| 厂商: | Microchip Technology |

| 文件页数: | 61/184页 |

| 文件大小: | 0K |

| 描述: | IC MCU OTP 4KX14 PWM 28SSOP |

| 标准包装: | 2,100 |

| 系列: | PIC® 16C |

| 核心处理器: | PIC |

| 芯体尺寸: | 8-位 |

| 速度: | 4MHz |

| 连通性: | I²C,SPI,UART/USART |

| 外围设备: | 欠压检测/复位,POR,PWM,WDT |

| 输入/输出数: | 22 |

| 程序存储器容量: | 7KB(4K x 14) |

| 程序存储器类型: | OTP |

| RAM 容量: | 192 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 4 V ~ 5.5 V |

| 振荡器型: | 外部 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 28-SSOP(0.209",5.30mm 宽) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页当前第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页

153

SAM7S Series [DATASHEET]

6175M–ATARM–26-Oct-12

Programming the Next Counter/Pointer registers chains the buffers. The counters are decremented after each data

transfer as stated above, but when the transfer counter reaches zero, the values of the Next Counter/Pointer are

loaded into the Counter/Pointer registers in order to re-enable the triggers.

For each channel, two status bits indicate the end of the current buffer (ENDRX, ENDTX) and the end of both cur-

rent and next buffer (RXBUFF, TXBUFE). These bits are directly mapped to the peripheral status register and can

trigger an interrupt request to the AIC.

The peripheral end flag is automatically cleared when one of the counter-registers (Counter or Next Counter Reg-

ister) is written.

Note: When the Next Counter Register is loaded into the Counter Register, it is set to zero.

22.3.4

Data Transfers

The peripheral triggers PDC transfers using transmit (TXRDY) and receive (RXRDY) signals.

When the peripheral receives an external character, it sends a Receive Ready signal to the PDC which then

requests access to the system bus. When access is granted, the PDC starts a read of the peripheral Receive Hold-

ing Register (RHR) and then triggers a write in the memory.

After each transfer, the relevant PDC memory pointer is incremented and the number of transfers left is decre-

mented. When the memory block size is reached, a signal is sent to the peripheral and the transfer stops.

The same procedure is followed, in reverse, for transmit transfers.

22.3.5

Priority of PDC Transfer Requests

The Peripheral DMA Controller handles transfer requests from the channel according to priorities fixed for each

product.These priorities are defined in the product datasheet.

If simultaneous requests of the same type (receiver or transmitter) occur on identical peripherals, the priority is

determined by the numbering of the peripherals.

If transfer requests are not simultaneous, they are treated in the order they occurred. Requests from the receivers

are handled first and then followed by transmitter requests.

22.4

Peripheral DMA Controller (PDC) User Interface

Note:

1. PERIPH: Ten registers are mapped in the peripheral memory space at the same offset. These can be defined by the user

according to the function and the peripheral desired (DBGU, USART, SSC, SPI, MCI etc).

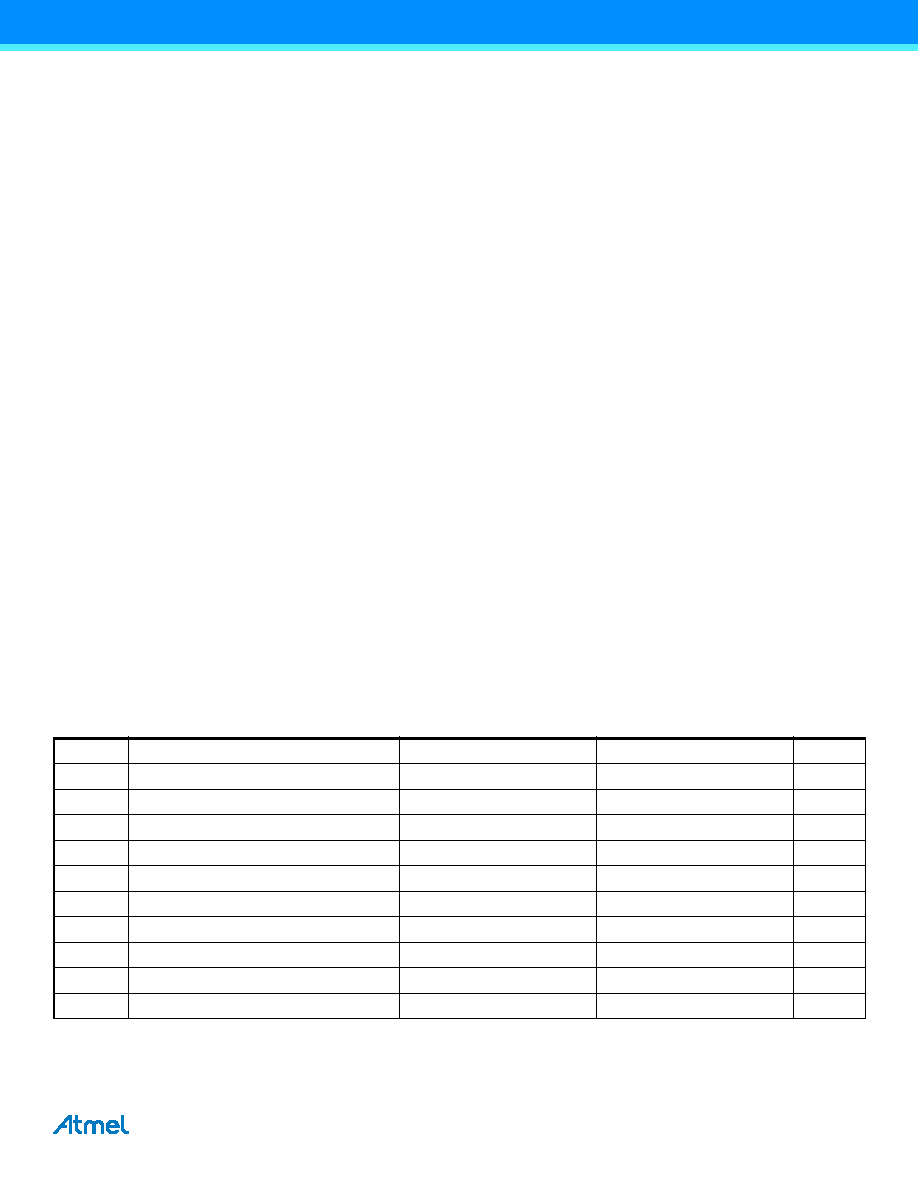

Table 22-1.

Register Mapping

Offset

Register

Register Name

Access

Reset

0x100

Receive Pointer Register

PERIPH(1)_RPR

Read-write

0x0

0x104

Receive Counter Register

PERIPH_RCR

Read-write

0x0

0x108

Transmit Pointer Register

PERIPH_TPR

Read-write

0x0

0x10C

Transmit Counter Register

PERIPH_TCR

Read-write

0x0

0x110

Receive Next Pointer Register

PERIPH_RNPR

Read-write

0x0

0x114

Receive Next Counter Register

PERIPH_RNCR

Read-write

0x0

0x118

Transmit Next Pointer Register

PERIPH_TNPR

Read-write

0x0

0x11C

Transmit Next Counter Register

PERIPH_TNCR

Read-write

0x0

0x120

PDC Transfer Control Register

PERIPH_PTCR

Write-only

-

0x124

PDC Transfer Status Register

PERIPH_PTSR

Read-only

0x0

相关PDF资料 |

PDF描述 |

|---|---|

| PIC16C63AT-04E/SO | IC MCU OTP 4KX14 PWM 28SOIC |

| VE-B6Z-IV-F2 | CONVERTER MOD DC/DC 2V 60W |

| PIC16C63A-04E/SS | IC MCU OTP 4KX14 PWM 28SSOP |

| VE-B6Y-IV-F4 | CONVERTER MOD DC/DC 3.3V 99W |

| PIC16C63A-04E/SP | IC MCU OTP 4KX14 PWM 28DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PIC16C63AT-04I/SO | 功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16C63AT-04I/SS | 功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16C63AT-20/SO | 功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16C63AT-20/SS | 功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16C63AT-20E/SO | 功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。