- 您现在的位置:买卖IC网 > PDF目录11590 > PIC16F688-E/SL (Microchip Technology)IC MCU PIC FLASH 4KX14 14SOIC PDF资料下载

参数资料

| 型号: | PIC16F688-E/SL |

| 厂商: | Microchip Technology |

| 文件页数: | 19/204页 |

| 文件大小: | 0K |

| 描述: | IC MCU PIC FLASH 4KX14 14SOIC |

| 产品培训模块: | Asynchronous Stimulus |

| 标准包装: | 57 |

| 系列: | PIC® 16F |

| 核心处理器: | PIC |

| 芯体尺寸: | 8-位 |

| 速度: | 20MHz |

| 连通性: | UART/USART |

| 外围设备: | 欠压检测/复位,POR,WDT |

| 输入/输出数: | 12 |

| 程序存储器容量: | 7KB(4K x 14) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 256 x 8 |

| RAM 容量: | 256 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2 V ~ 5.5 V |

| 数据转换器: | A/D 8x10b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 14-SOIC(0.154",3.90mm 宽) |

| 包装: | 管件 |

| 配用: | XLT14SO-1-ND - SOCKET TRANSITION 14SOIC 150/208 AC162061-ND - HEADER INTRFC MPLAB ICD2 20PIN AC162056-ND - HEADER INTERFACE ICD2 16F688 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页

2009 Microchip Technology Inc.

DS41203E-page 113

PIC16F688

11.2.1

POWER-ON RESET

The on-chip POR circuit holds the chip in Reset until

VDD has reached a high enough level for proper

operation. To take advantage of the POR, simply

connect the MCLR pin through a resistor to VDD. This

will eliminate external RC components usually needed

to create Power-on Reset. A maximum rise time for

cations” for details. If the BOR is enabled, the maxi-

mum rise time specification does not apply. The BOR

circuitry will keep the device in Reset until VDD reaches

VBOD

(see

(BOR)”).

When the device starts normal operation (exits the

Reset condition), device operating parameters (i.e.,

voltage, frequency, temperature, etc.) must be met to

ensure operation. If these conditions are not met, the

device must be held in Reset until the operating

conditions are met.

For additional information, refer to Application Note

AN607, “Power-up Trouble Shooting” (DS00607).

11.2.2

MCLR

PIC16F688 has a noise filter in the MCLR Reset path.

The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive

MCLR pin low.

The behavior of the ESD protection on the MCLR pin

has been altered from early devices of this family.

Voltages applied to the pin that exceed its specification

can result in both MCLR Resets and excessive current

beyond the device specification during the ESD event.

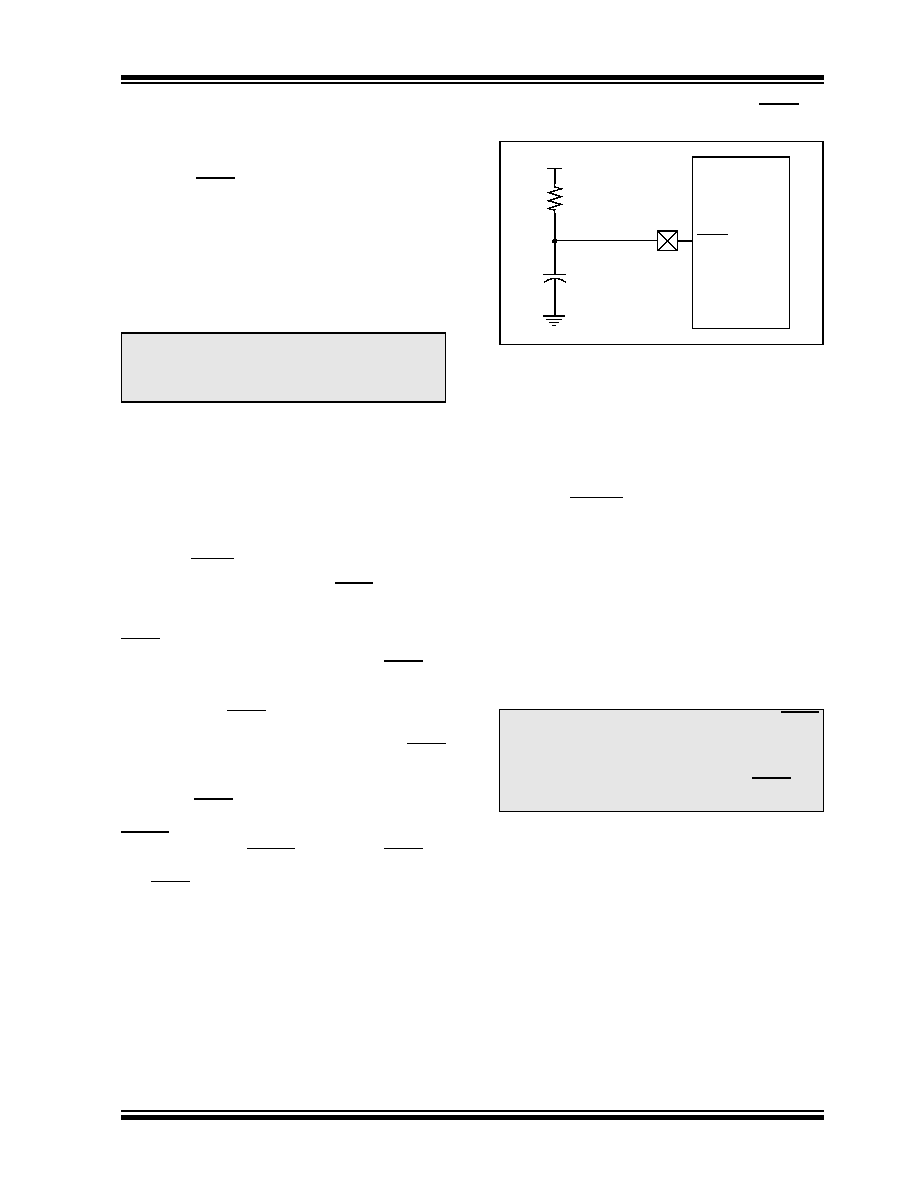

For this reason, Microchip recommends that the MCLR

pin no longer be tied directly to VDD. The use of an RC

network, as shown in Figure 11-2, is suggested.

An internal MCLR option is enabled by clearing the

MCLRE bit in the Configuration Word register. When

MCLRE = 0, the Reset signal to the chip is generated

internally. When the MCLRE = 1, the RA3/MCLR pin

becomes an external Reset input. In this mode, the

RA3/MCLR pin has a weak pull-up to VDD.

FIGURE 11-2:

RECOMMENDED MCLR

CIRCUIT

11.2.3

POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 64 ms (nominal)

time-out on power-up only, from POR or Brown-out

Reset. The Power-up Timer operates from the 31 kHz

LFINTOSC oscillator. For more information, see

Section 3.5 “Internal Clock Modes”. The chip is kept

in Reset as long as PWRT is active. The PWRT delay

allows the VDD to rise to an acceptable level. A Config-

uration bit, PWRTE, can disable (if set) or enable (if

cleared or programmed) the Power-up Timer. The

Power-up Timer should be enabled when Brown-out

Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip

and vary due to:

VDD variation

Temperature variation

Process variation

See

DC

parameters

for

details

Note:

The POR circuit does not produce an

internal Reset when VDD declines. To

re-enable the POR, VDD must reach Vss

for a minimum of 100

μs.

Note:

Voltage spikes below VSS at the MCLR

pin, inducing currents greater than 80 mA,

may cause latch-up. Thus, a series resis-

tor of 50-100 Ω should be used when

applying a “low” level to the MCLR pin,

rather than pulling this pin directly to VSS.

VDD

PIC16F688

MCLR

R1

1k

Ω (or greater)

C1

0.1

μF

(optional, not critical)

相关PDF资料 |

PDF描述 |

|---|---|

| V110C3V3M50BF3 | CONVERTER MOD DC/DC 3.3V 50W |

| PIC16F636-E/ST | IC MCU FLASH 2KX14 14TSSOP |

| V72A48C400BG3 | CONVERTER MOD DC/DC 48V 400W |

| VI-B6P-IW-F2 | CONVERTER MOD DC/DC 13.8V 100W |

| PIC16F684T-I/ST | IC PIC MCU FLASH 2KX14 14TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PIC16F688-I/ML | 功能描述:8位微控制器 -MCU 7KB 256 RAM 12I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16F688-I/P | 功能描述:8位微控制器 -MCU 7KB 256 RAM 12 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16F688-I/P | 制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 16F688 DIP14 |

| PIC16F688-I/P | 制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 16F688 DIP14 制造商:Microchip Technology Inc 功能描述:IC, 8BIT FLASH MCU, 16F688, DIP14 制造商:Microchip Technology Inc 功能描述:IC, 8BIT FLASH MCU, 16F688, DIP14; Controller Family/Series:PIC16F; Core Size:8bit; No. of I/O's:12; Supply Voltage Min:2V; Supply Voltage Max:5.5V; Digital IC Case Style:DIP; No. of Pins:14; Program Memory Size:4Kwords; EEPROM ;RoHS Compliant: Yes |

| PIC16F688-I/P-ND | 制造商:Microchip Technology Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。