- 您现在的位置:买卖IC网 > PDF目录11557 > PIC16F716T-E/SS (Microchip Technology)IC PIC MCU FLASH 2KX14 20SSOP PDF资料下载

参数资料

| 型号: | PIC16F716T-E/SS |

| 厂商: | Microchip Technology |

| 文件页数: | 100/136页 |

| 文件大小: | 0K |

| 描述: | IC PIC MCU FLASH 2KX14 20SSOP |

| 产品培训模块: | Asynchronous Stimulus |

| 标准包装: | 1,600 |

| 系列: | PIC® 16F |

| 核心处理器: | PIC |

| 芯体尺寸: | 8-位 |

| 速度: | 20MHz |

| 外围设备: | 欠压检测/复位,POR,PWM,WDT |

| 输入/输出数: | 13 |

| 程序存储器容量: | 3.5KB(2K x 14) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 128 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 3 V ~ 5.5 V |

| 数据转换器: | A/D 4x8b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 20-SSOP(0.209",5.30mm 宽) |

| 包装: | 带卷 (TR) |

| 配用: | I3-DB16F716-ND - BOARD DAUGHTER ICEPIC3 AC162054-ND - HEADER INTERFACE ICD2 16F716 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页当前第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页

PIC16F716

DS41206B-page 64

2007 Microchip Technology Inc.

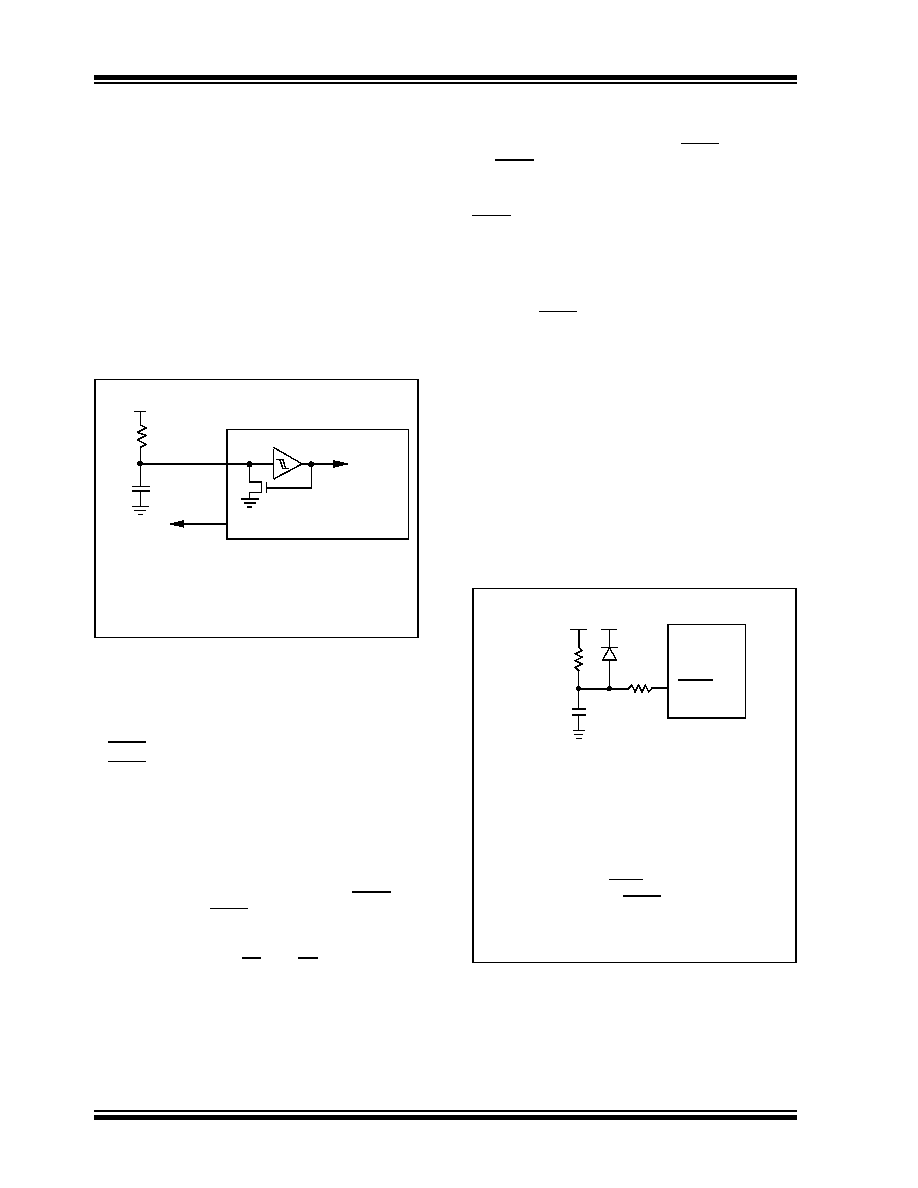

9.2.3

RC OSCILLATOR

For timing insensitive applications, the “RC” device

option offers additional cost savings. The RC oscillator

frequency is a function of the supply voltage, the

resistor (REXT) and capacitor (CEXT) values and the

operating temperature. In addition to this, the oscillator

frequency will vary from unit-to-unit due to normal

process

parameter

variation.

Furthermore,

the

difference in lead frame capacitance between package

types will also affect the oscillation frequency,

especially for low CEXT values. The user also needs to

take into account variation due to tolerance of external

R and C components used. Figure 9-3 shows how the

R/C combination is connected to the PIC16F716.

FIGURE 9-3:

RC OSCILLATOR MODE

9.3

Reset

The PIC16F716 differentiates between various kinds of

Reset:

Power-on Reset (POR)

MCLR Reset during normal operation

MCLR Reset during Sleep

WDT Reset (during normal operation)

WDT Wake-up (during Sleep)

Brown-out Reset (BOR)

Some registers are not affected in any Reset condition;

their status is unknown on POR and unchanged in any

other Reset. Most other registers are reset to a “Reset

state” on Power-on Reset (POR), on the MCLR and

WDT Reset, on MCLR Reset during Sleep and

Brown-out Reset (BOR). They are not affected by a

WDT Wake-up, which is viewed as the resumption of

normal operation. The TO and PD bits are set or

cleared differently in different Reset situations as indi-

cated in Table 9-4. These bits are used in software to

determine the nature of the Reset. See Table 9-6 for a

full description of Reset states of all registers.

A simplified block diagram of the On-chip Reset circuit

is shown in Figure 9-5.

The PIC microcontrollers have an MCLR noise filter in

the MCLR Reset path. The filter will detect and ignore

small pulses.

It should be noted that a WDT Reset does not drive the

MCLR pin low.

9.4

Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when

VDD rise is detected. To take advantage of the POR,

just tie the MCLR pin directly (or through a resistor) to

VDD. This will eliminate external RC components

usually needed to create a Power-on Reset. A

maximum rise time for VDD is specified (parameter

D004). For a slow rise time, see Figure 9-4.

When the device starts normal operation (exits the

Reset

condition),

device

operating

parameters

(voltage, frequency, temperature,...) must be met to

ensure operation. If these conditions are not met, the

device must be held in Reset until the operating

conditions are met. Brown-out Reset may be used to

meet the start-up conditions.

FIGURE 9-4:

EXTERNAL POWER-ON

RESET CIRCUIT (FOR

SLOW VDD POWER-UP)

OSC2/CLKOUT

CEXT

REXT

PIC16F716

OSC1

FOSC/4

Internal

clock

VDD

VSS

Recommended values:

3k

Ω ≤ REXT ≤ 100 kΩ (VDD ≥ 3.0V)

10 k

Ω ≤ REXT ≤ 100 kΩ (VDD ≥ 3.0V)

CEXT

> 20 pF

Note 1:

External Power-on Reset circuit is required

only if VDD power-up slope is too slow. The

diode D helps discharge the capacitor quickly

when VDD powers down.

2:

R < 40 k

Ω is recommended to make sure that

voltage drop across R does not violate the

device’s electrical specification.

3:

R1 = 100

Ω to 1 kΩ will limit any current

flowing into MCLR from external capacitor C

in the event of MCLR/VPP pin breakdown due

to Electrostatic Discharge (ESD) or Electrical

Overstress

(EOS).

C

R1

R

VDD

MCLR

PIC16F716

VDD

相关PDF资料 |

PDF描述 |

|---|---|

| GRM2165C1H561JA01D | CAP CER 560PF 50V 5% NP0 0805 |

| V375A36C400BL3 | CONVERTER MOD DC/DC 36V 400W |

| 2-227079-0 | CONN PLUG BNC 50 OHM DUAL CRIMP |

| V375A36C400BL2 | CONVERTER MOD DC/DC 36V 400W |

| PIC16F726-E/MV | IC MCU 8BIT 14KB FLASH 28UQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PIC16F716T-I/ML | 制造商:Microchip Technology Inc 功能描述:MCU 8BIT RISC 28KB FLASH 2.5V/ - Tape and Reel |

| PIC16F716T-I/SO | 功能描述:8位微控制器 -MCU 3.5KB 128 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16F716T-I/SS | 功能描述:8位微控制器 -MCU 3.5KB 128 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16F716T-I/SS045 | 制造商:Microchip Technology Inc 功能描述: |

| PIC16F716T-I/SS056 | 制造商:Microchip Technology Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。