- 您现在的位置:买卖IC网 > PDF目录3883 > PIC18LF248T-I/SO (Microchip Technology)IC MCU FLASH 8KX16 LV CAN 28SOIC PDF资料下载

参数资料

| 型号: | PIC18LF248T-I/SO |

| 厂商: | Microchip Technology |

| 文件页数: | 29/116页 |

| 文件大小: | 0K |

| 描述: | IC MCU FLASH 8KX16 LV CAN 28SOIC |

| 标准包装: | 1,600 |

| 系列: | PIC® 18F |

| 核心处理器: | PIC |

| 芯体尺寸: | 8-位 |

| 速度: | 40MHz |

| 连通性: | CAN,I²C,SPI,UART/USART |

| 外围设备: | 欠压检测/复位,LVD,POR,PWM,WDT |

| 输入/输出数: | 22 |

| 程序存储器容量: | 16KB(8K x 16) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 256 x 8 |

| RAM 容量: | 768 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2 V ~ 5.5 V |

| 数据转换器: | A/D 5x10b |

| 振荡器型: | 外部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 28-SOIC(0.295",7.50mm 宽) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页

PIC18FXX8

DS41159E-page 26

2006 Microchip Technology Inc.

3.1

Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when a

VDD rise is detected. To take advantage of the POR

circuitry, connect the MCLR pin directly (or through a

resistor) to VDD. This eliminates external RC compo-

nents usually needed to create a Power-on Reset

delay. A minimum rise rate for VDD is specified (refer to

parameter D004). For a slow rise time, see Figure 3-2.

When the device starts normal operation (exits the

Reset

condition),

device

operating

parameters

(voltage, frequency, temperature, etc.) must be met to

ensure operation. If these conditions are not met, the

device must be held in Reset until the operating condi-

tions are met. Brown-out Reset may be used to meet

the voltage start-up condition.

3.2

MCLR

PIC18FXX8 devices have a noise filter in the MCLR

Reset path. The filter will detect and ignore small

pulses.

It should be noted that a WDT Reset does not drive

MCLR pin low.

The behavior of the ESD protection on the MCLR pin

differs from previous devices of this family. Voltages

applied to the pin that exceed its specification can

result in both Resets and current draws outside of

device specification during the Reset event. For this

reason, Microchip recommends that the MCLR pin no

longer be tied directly to VDD. The use of an RC

network, as shown in Figure 3-2, is suggested.

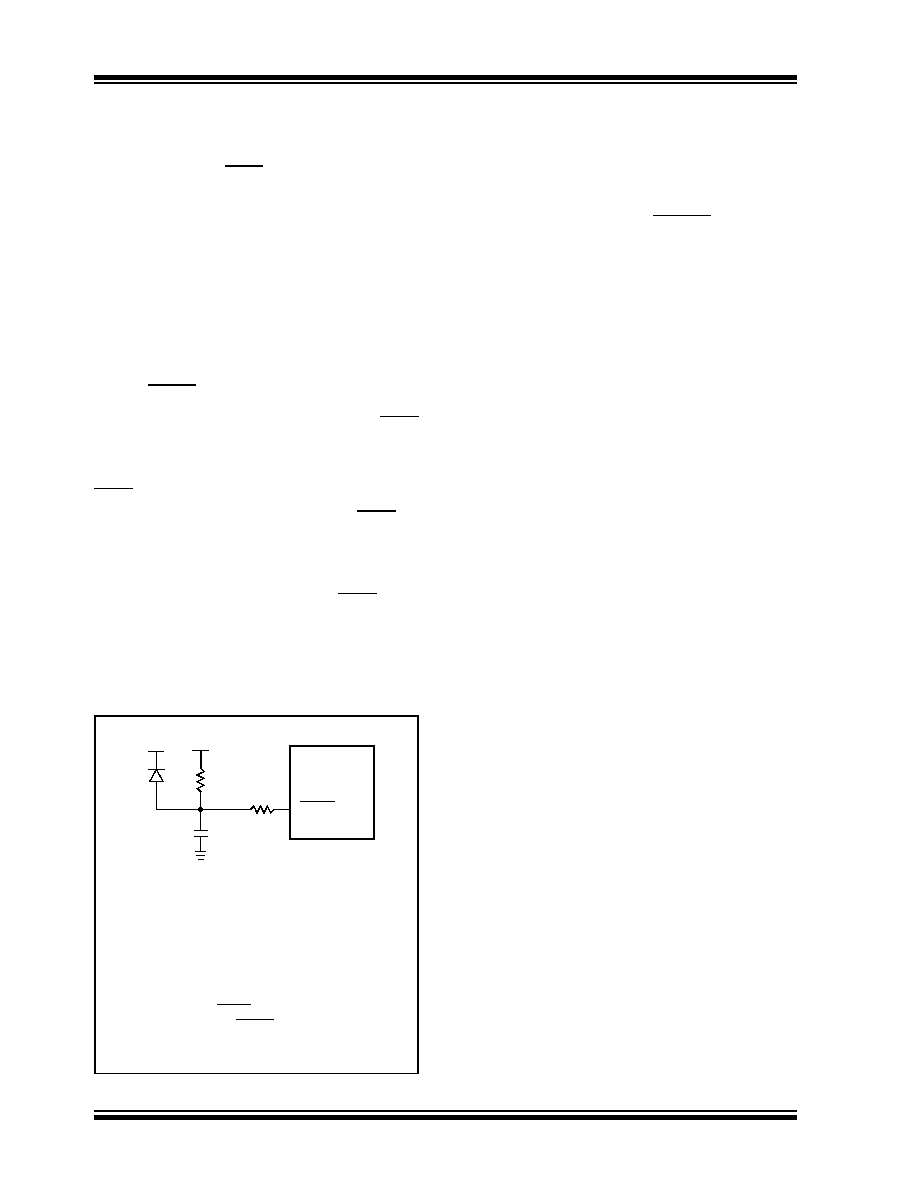

FIGURE 3-2:

EXTERNAL POWER-ON

RESET CIRCUIT (FOR

SLOW VDD POWER-UP)

3.3

Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out

(parameter #33), only on power-up from the POR. The

Power-up Timer operates on an internal RC oscillator.

The chip is kept in Reset as long as the PWRT is active.

The PWRT’s time delay allows VDD to rise to an accept-

able level. A configuration bit (PWRTEN in CONFIG2L

register) is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due

to VDD, temperature and process variation. See DC

parameter #33 for details.

3.4

Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024

oscillator cycle (from OSC1 input) delay after the

PWRT delay is over (parameter #32). This additional

delay ensures that the crystal oscillator or resonator

has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and

HS4 modes and only on Power-on Reset or wake-up

from Sleep.

3.5

PLL Lock Time-out

With the PLL enabled, the time-out sequence following

a Power-on Reset is different from other oscillator

modes. A portion of the Power-up Timer is used to pro-

vide a fixed time-out that is sufficient for the PLL to lock

to the main oscillator frequency. This PLL lock time-out

(TPLL) is typically 2 ms and follows the oscillator

start-up time-out (OST).

3.6

Brown-out Reset (BOR)

A configuration bit, BOREN, can disable (if clear/

programmed), or enable (if set), the Brown-out Reset

circuitry. If VDD falls below parameter D005 for greater

than parameter #35, the brown-out situation resets the

chip. A Reset may not occur if VDD falls below param-

eter D005 for less than parameter #35. The chip will

remain in Brown-out Reset until VDD rises above BVDD.

The Power-up Timer will then be invoked and will keep

the chip in Reset an additional time delay (parameter

#33). If VDD drops below BVDD while the Power-up

Timer is running, the chip will go back into a Brown-out

Reset and the Power-up Timer will be initialized. Once

VDD rises above BVDD, the Power-up Timer will

execute the additional time delay.

Note

1: External Power-on Reset circuit is required

only if the VDD power-up slope is too slow.

The diode D helps discharge the capacitor

quickly when VDD powers down.

2: R < 40 k

Ω is recommended to make sure that

the voltage drop across R does not violate

the device’s electrical specification.

3: R1 = 100

Ω to 1 kΩ will limit any current flow-

ing into MCLR from external capacitor C, in

the event of MCLR/VPP pin breakdown due to

Electrostatic Discharge (ESD) or Electrical

Overstress (EOS).

C

R1

R

D

VDD

MCLR

PIC18FXXX

相关PDF资料 |

PDF描述 |

|---|---|

| PIC16C62BT-20I/ML | IC MCU OTP 2KX14 28-QFN |

| PIC16C63AT-20I/ML | IC MCU OTP 4KX14 28-QFN |

| PIC16C73BT-20I/ML | IC MCU OTP 4KX14 28-QFN |

| PIC16F876AT-E/SO | IC MCU FLASH 8KX14 W/AD 28-SOIC |

| PIC16C72AT-20I/ML | IC MCU OTP 2KX14 28-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PIC18LF24J10-I/ML | 功能描述:8位微控制器 -MCU 16 KB FL 1024 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC18LF24J10-I/SO | 功能描述:8位微控制器 -MCU 16 KB FL 1024 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC18LF24J10-I/SP | 功能描述:8位微控制器 -MCU 16 KB FL 1024 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC18LF24J10-I/SS | 功能描述:8位微控制器 -MCU 16 KB FL 1024 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC18LF24J10T-I/ML | 功能描述:8位微控制器 -MCU 16 KB FL 1024 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。