- 您现在的位置:买卖IC网 > PDF目录3816 > PIC32MX320F128L-80V/BG (Microchip Technology)IC MCU 32BIT 128KB FLSH 121XBGA PDF资料下载

参数资料

| 型号: | PIC32MX320F128L-80V/BG |

| 厂商: | Microchip Technology |

| 文件页数: | 148/214页 |

| 文件大小: | 0K |

| 描述: | IC MCU 32BIT 128KB FLSH 121XBGA |

| 标准包装: | 184 |

| 系列: | PIC® 32MX |

| 核心处理器: | MIPS32? M4K? |

| 芯体尺寸: | 32-位 |

| 速度: | 80MHz |

| 连通性: | I²C,IrDA,LIN,PMP,SPI,UART/USART |

| 外围设备: | 欠压检测/复位,POR,PWM,WDT |

| 程序存储器容量: | 128KB(128K x 8) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 16K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2.3 V ~ 3.6 V |

| 数据转换器: | A/D 16x10b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 105°C |

| 封装/外壳: | 121-TFBGA |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页当前第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页

2011 Microchip Technology Inc.

DS61143H-page 39

PIC32MX3XX/4XX

The MIPS architecture defines that the result of a mul-

tiply or divide operation be placed in the HI and LO reg-

isters. Using the Move-From-HI (MFHI) and Move-

From-LO (MFLO) instructions, these values can be

transferred to the general purpose register file.

In addition to the HI/LO targeted operations, the

MIPS32 architecture also defines a multiply instruction,

MUL, which places the least significant results in the

primary register file instead of the HI/LO register pair.

By avoiding the explicit MFLO instruction, required

when using the LO register, and by supporting multiple

destination

registers,

the

throughput

of

multiply-intensive operations is increased.

Two other instructions, multiply-add (MADD) and multi-

ply-subtract (MSUB), are used to perform the multiply-

accumulate and multiply-subtract operations. The

MADD

instruction multiplies two numbers and then adds

the product to the current contents of the HI and LO

registers. Similarly, the MSUB instruction multiplies two

operands and then subtracts the product from the HI

and LO registers. The MADD and MSUB operations

are commonly used in DSP algorithms.

3.2.3

SYSTEM CONTROL

COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the vir-

tual-to-physical address translation, the exception con-

trol system, the processor’s diagnostics capability, the

operating modes (kernel, user and debug), and

whether interrupts are enabled or disabled. Configura-

tion information, such as presence of options like

MIPS16e, is also available by accessing the CP0

registers, listed in Table 3-2.

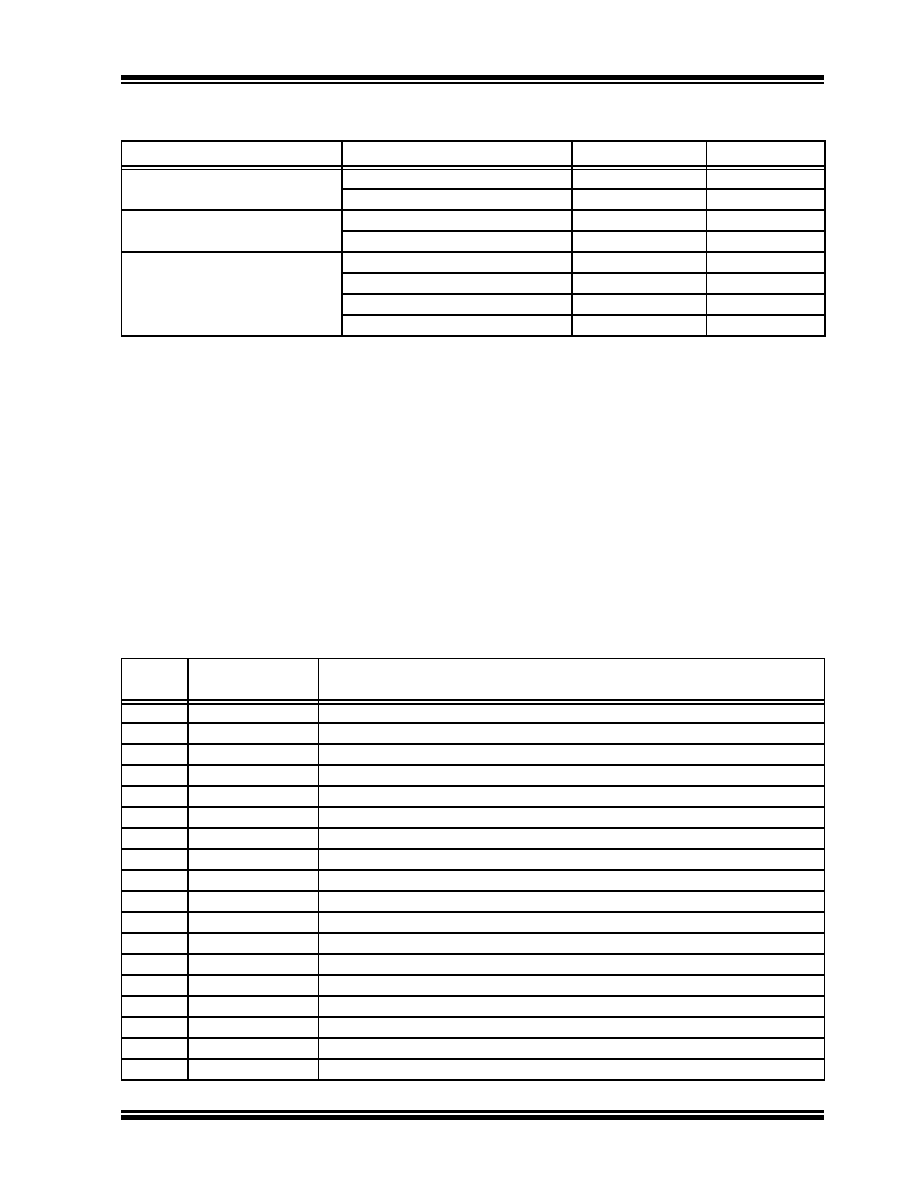

TABLE 3-1:

MIPS M4K PROCESSOR CORE HIGH-PERFORMANCE INTEGER

MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

Opcode

Operand Size (mul rt) (div rs)

Latency

Repeat Rate

MULT/MULTU, MADD/MADDU,

MSUB/MSUBU

16 bits

1

32 bits

2

MUL

16 bits

2

1

32 bits

3

2

DIV/DIVU

8 bits

12

11

16 bits

19

18

24 bits

26

25

32 bits

33

32

TABLE 3-2:

COPROCESSOR 0 REGISTERS

Register

Number

Register

Name

Function

0-6

Reserved

7

HWREna

Enables access via the RDHWR instruction to selected hardware registers

8

BadVAddr(1)

Reports the address for the most recent address-related exception

9

Count(1)

Processor cycle count

10

Reserved

11

Compare(1)

Timer interrupt control

12

Status(1)

Processor status and control

12

IntCtl(1)

Interrupt system status and control

12

SRSCtl(1)

Shadow register set status and control

12

SRSMap(1)

Provides mapping from vectored interrupt to a shadow set

13

Cause(1)

Cause of last general exception

14

EPC(1)

Program counter at last exception

15

PRId

Processor identification and revision

15

EBASE

Exception vector base register

16

Config

Configuration register

16

Config1

Configuration register 1

16

Config2

Configuration register 2

16

Config3

Configuration register 3

相关PDF资料 |

PDF描述 |

|---|---|

| PIC16C67-20/L | IC MCU OTP 8KX14 PWM 44PLCC |

| PIC16LF877-04I/P | IC MCU FLASH 8KX14 EE A/D 40DIP |

| PIC18F442-I/L | IC MCU FLASH 8KX16 EE A/D 44PLCC |

| PIC16F874-04/L | IC MCU FLASH 4KX14 EE 44PLCC |

| PIC18F6527-I/PT | IC PIC MCU FLASH 24KX16 64TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PIC32MX320F128LT-80I/BG | 功能描述:32位微控制器 - MCU 128KB Flash 32KB RAM 80MHz 10B ADC RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT |

| PIC32MX320F128LT-80I/PT | 功能描述:32位微控制器 - MCU 100Pin, 128 KB Flash 32 KB RAM,10-Bit ADC RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT |

| PIC32MX320F128LT-80V/BG | 功能描述:32位微控制器 - MCU 128 KB FL 16 KB RAM 80MHz 10-Bit ADC DMA RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT |

| PIC32MX320F128LT-80V/PT | 功能描述:32位微控制器 - MCU 128 KB FL 16 KB RAM 80MHz 10-Bit ADC DMA RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT |

| PIC32MX330F064H-I/MR | 制造商:Microchip Technology Inc 功能描述:80MHZ, 64KB FLASH, 16 KB RAM, CTMU, I2S, DMA, USB-OTG - Rail/Tube 制造商:Microchip Technology Inc 功能描述:IC MCU 32BIT 64KB FLASH 64QFN 制造商:Microchip Technology Inc 功能描述:80MHz, 64KB Flash, 16 KB RAM, CTMU, I2S, DMA, USB-OTG, 64 QFN 9x9x0.9mm TUBE |

发布紧急采购,3分钟左右您将得到回复。