- 您现在的位置:买卖IC网 > PDF目录370005 > PLC18V8Z25N (NXP SEMICONDUCTORS) Zero standby power CMOS versatile PAL devices PDF资料下载

参数资料

| 型号: | PLC18V8Z25N |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | PLD |

| 英文描述: | Zero standby power CMOS versatile PAL devices |

| 中文描述: | OT PLD, 25 ns, PDIP20 |

| 封装: | 0.300 INCH, PLASTIC, SOT-146-1, DIP-20 |

| 文件页数: | 10/23页 |

| 文件大小: | 225K |

| 代理商: | PLC18V8Z25N |

Philips Semiconductors

Product specification

PLC18V8Z

Zero standby power

CMOS versatile PAL devices

1997 Aug 08

10

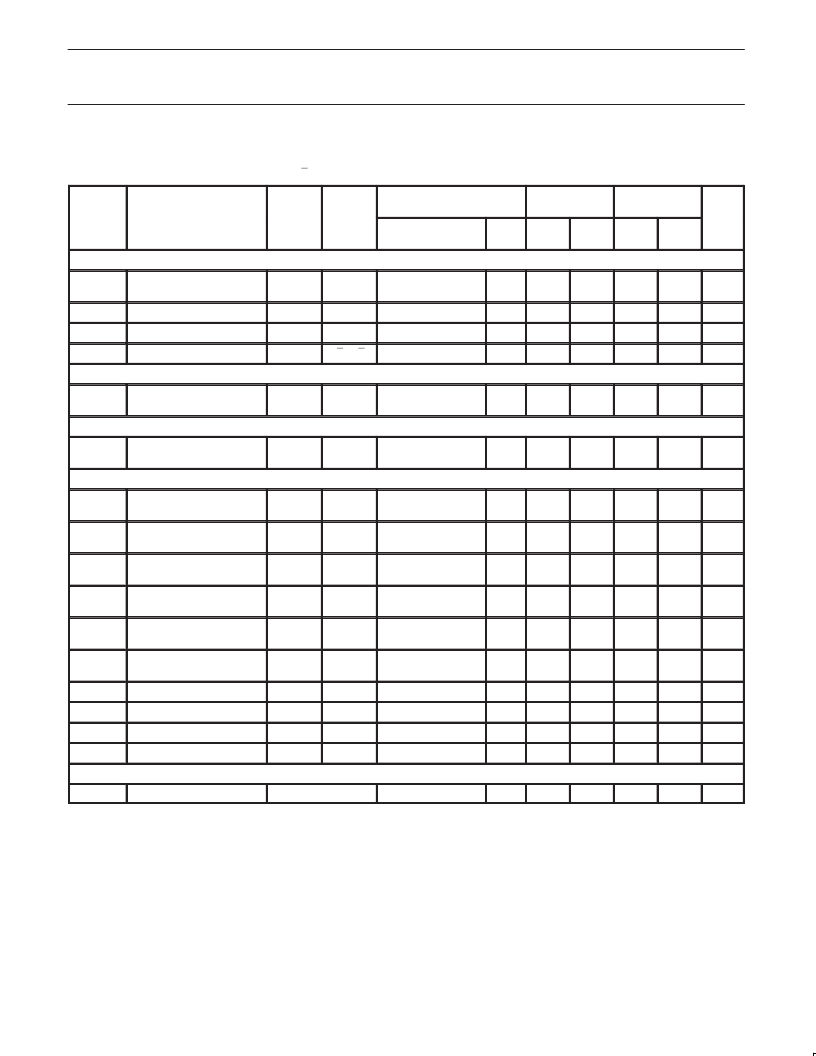

AC ELECTRICAL CHARACTERISTICS

4

Commercial = 0

°

C

≤

T

amb

≤

+75

°

C, 4.75V

≤

V

CC

< 5.25V;

Industrial = –40

°

C

≤

T

amb

≤

+85

°

C, 4.5V

≤

V

CC

≤

5.5V; R

2

= 390

TEST CONDITION

1

PLC18V8Z25

(Commercial)

PLC18V8ZIA

(Industrial)

SYMBOL

PARAMETER

FROM

TO

R

1

(

)

C

L

(pF)

MIN

MAX

MIN

MAX

UNIT

Pulse width

t

CKP

Clock period

(Minimum t

IS

+ t

CKO

)

CLK +

CLK +

200

50

33

33

ns

t

CKH

Clock width High

CLK +

CLK –

200

50

15

15

ns

t

CKL

Clock width Low

CLK –

CLK +

200

50

15

15

ns

t

ARW

Async reset pulse width

I

±

, F

±

I +, F +

25

25

ns

Hold time

t

IH

Input or feedback

data hold time

CLK +

Input

±

200

50

0

0

ns

Setup time

t

IS

Input or feedback

data setup time

I

±

, F

±

CLK +

200

50

18

18

ns

Propagation delay

t

PD

Delay from input

to active output

I

±

, F

±

F

±

200

50

25

25

ns

t

CKO

Clock High to output valid

access Time

CLK +

F

±

200

50

15

15

ns

t

OE13

Product term enable to

outputs off

I

±

, F

±

F

±

Active-High R = 1.5k

Active-Low R = 550

50

25

25

ns

t

OD12

Product term disable to

outputs off

I

±

, F

±

F

±

From V

OH

R =

∞

From V

OL

R = 200

From V

OH

R =

∞

From V

OL

R = 200

5

25

25

ns

t

OD22

Pin 11 output disable High

to outputs off

OE –

F

±

5

20

20

ns

t

OE23

Pin 11 output enable to

active output

OE +

F

±

Active-High R = 1.5k

Active-Low R = 550

50

20

20

ns

t

ARD

Async reset delay

I

±

, F

±

F +

30

30

ns

t

ARR

Async reset recovery time

I

±

, F

±

CLK +

20

20

ns

t

SPR

Sync preset recovery time

I

±

, F

±

CLK +

20

20

ns

t

PPR

Power-up reset

V

CC

+

F +

25

25

ns

Frequency of operation

f

MAX

NOTES:

1. Refer also to AC Test Conditions. (Test Load Circuit)

2. For 3-State output; output enable times are tested with C

= 50pF to the 1.5V level, and S

is open for high-impedance to High tests and

closed for high-impedance to Low tests. Output disable times are tested with C

= 5pF. High-to-High impedance tests are made to an output

voltage of V

= (V

– 0.5V) with S

open, and Low-to-High impedance tests are made to the V

= (V

+ 0.5V) level with S

closed.

3. Resistor values of 1.5k and 550

provide 3-State levels of 1.0V and 2.0V, respectively. Output timing measurements are to 1.5V level.

4. Leave all the cells on unused product terms intact (unprogrammed) for all patterns.

Maximum frequency

I/(t

IS

+ t

CKO

)

200

50

30

30

MHz

相关PDF资料 |

PDF描述 |

|---|---|

| PLC18V8Z35D | Zero standby power CMOS versatile PAL devices |

| PLC18V8Z35DB | Zero standby power CMOS versatile PAL devices |

| PLC18V8Z35DH | Zero standby power CMOS versatile PAL devices |

| PLC18V8Z35N | Zero standby power CMOS versatile PAL devices |

| PLC18V8ZIDH | Zero standby power CMOS versatile PAL devices |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PLC18V8Z35A | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Zero standby power CMOS versatile PAL devices |

| PLC18V8Z35D | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Zero standby power CMOS versatile PAL devices |

| PLC18V8Z35DB | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Zero standby power CMOS versatile PAL devices |

| PLC18V8Z35DH | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:Zero standby power CMOS versatile PAL devices |

| PLC18V8Z35N | 制造商:NXP Semiconductors 功能描述: |

发布紧急采购,3分钟左右您将得到回复。