- 您现在的位置:买卖IC网 > PDF目录370005 > PLDC20G10-25WC (CYPRESS SEMICONDUCTOR CORP) CMOS Generic 24-Pin Reprogrammable Logic Device PDF资料下载

参数资料

| 型号: | PLDC20G10-25WC |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | CMOS Generic 24-Pin Reprogrammable Logic Device |

| 中文描述: | UV PLD, 25 ns, CDIP24 |

| 封装: | 0.300 INCH, WINDOWED, CERDIP-24 |

| 文件页数: | 1/14页 |

| 文件大小: | 393K |

| 代理商: | PLDC20G10-25WC |

USE ULTRA37000 FOR

ALL NEW DESIGNS

CMOS Generic 24-Pin Reprogrammable

Logic Device

PLDC20G10B

PLDC20G10

Cypress Semiconductor Corporation

Document #: 38-03010 Rev. *A

3901 North First Street

San Jose

,

CA 95134

408-943-2600

Revised April 20, 2004

Features

Fast

— Commercial: t

PD

= 15 ns, t

CO

= 10 ns, t

S

= 12 ns

— Military: t

PD

= 20 ns, t

CO

= 15 ns, t

S

= 15 ns

Low power

— I

CC

max.: 70 mA, commercial

— I

CC

max.: 100 mA, military

Commercial and military temperature range

User-programmable output cells

— Selectable for registered or combinatorial operation

— Output polarity control

— Output enable source selectable from pin 13 or

product term

Generic architecture to replace standard logic

functions including: 20L10, 20L8, 20R8, 20R6, 20R4,

12L10, 14L8, 16L6, 18L4, 20L2, and 20V8

Eight product terms and one OE product term per output

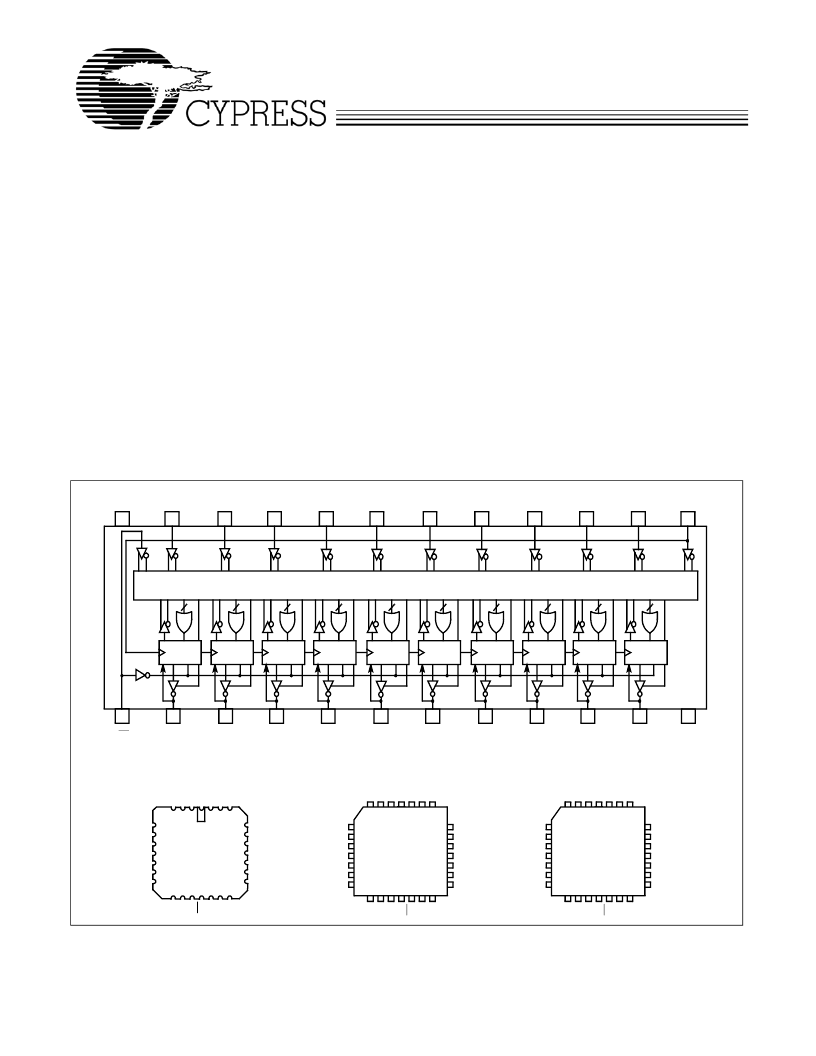

Logic Block Diagram

I

V

SS

I

CMOS EPROM technology for reprogrammability

Highly reliable

— Uses proven EPROM technology

— Fully AC and DC tested

— Security feature prevents logic pattern duplication

—

±

10% power supply voltage and higher noise

immunity

Functional Description

Cypress PLD devices are high-speed electrically program-

mable logic devices. These devices utilize the sum-of-products

(AND-OR) structure providing users the ability to program

custom logic functions for unique requirements.

In an unprogrammed state the AND gates are connected via

EPROM cells to both the true and complement of every input.

By selectively programming the EPROM cells, AND gates may

be connected to either the true or complement or disconnected

from both true and complement inputs.

Note:

1. The CG7C323 is the PLDC20G10 packaged in the JEDEC-compatible 28-pin PLCC pinout. Pin function and pin order is identical for both PLCC pinouts. The

difference is in the location of the “no connect” or NC pins.

PinConfigurations

8

9

8

7

6

5

4

3

2

1

10

15

16

17

18

19

20

21

22

23

24

PANDARRAY

I

I

I

I

I

I

I

I

CP/I

OUTPUT

CELL

8

OUTPUT

CELL

8

OUTPUT

CELL

O

O

O

8

O

OUTPUT

CELL

8

O

OUTPUT

CELL

8

O

OUTPUT

CELL

8

O

OUTPUT

CELL

8

O

OUTPUT

CELL

V

CC

11

12

13

14

I/OE

8

OUTPUT

CELL

8

OUTPUT

CELL

I/O

9

I/O

8

I/O

7

I/O

6

I/O

5

I/O

4

I/O

3

I/O

2

I/O

1

I/O

0

5

6

7

8

9

10

11

4 3 2

282726

12131415161718

25

24

23

22

21

20

19

I

I

I

I

I

I

NC

25

24

23

22

21

20

19

5

6

7

8

9

10

11121314 1516 1718

4 3 2

2827 26

I

I

I

I

I

I

N

9

I

I

I

V

I

I

8

I

V

I

I

S

I

I

C

V

I

I

0

1

0

1

C

C

9

I

8

I

V

I

I

S

1

1

C

N

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

NC

I

N

PLDC20G10

PLDC20G10B

25

24

23

22

21

20

19

5

6

7

8

9

10

11121314 1516 1718

4 3 2

2827 26

NC

I

I

I

I

NC

I

I

C

V

I

I

0

1

C

9

I

8

I

I

I

1

V

I

NC

I

I

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

NC

JEDEC PLCC

Top View

STD PLCC

Top View

LCC

Top View

I/O

2

I/O

3

I/O

4

NC

I/O

5

I/O

6

I/O

7

N

I

PLDC20G10

PLDC20G10B

CG7C323–A

CG7C323B–A

NC

[1]

相关PDF资料 |

PDF描述 |

|---|---|

| PLDC20G10-30DMB | CMOS Generic 24-Pin Reprogrammable Logic Device |

| PLDC20G10-30LMB | CMOS Generic 24-Pin Reprogrammable Logic Device |

| PLDC20G10-30WMB | CMOS Generic 24-Pin Reprogrammable Logic Device |

| PLDC20G10-35JC | CMOS Generic 24-Pin Reprogrammable Logic Device |

| PLDC20G10-35PC | CMOS Generic 24-Pin Reprogrammable Logic Device |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PLDC20G10-25WI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UV-Erasable/OTP PLD |

| PLDC20G10-30DMB | 制造商:Cypress Semiconductor 功能描述: |

| PLDC20G10-30LMB | 制造商:Cypress Semiconductor 功能描述:SPLD PLDC20G10 Family 400 Gates 10 Macro Cells 31.25MHz 5V 28-Pin LLCC |

| PLDC20G10-30WMB | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:CMOS Generic 24-Pin Reprogrammable Logic Device |

| PLDC20G10-35HC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UV-Erasable/OTP PLD |

发布紧急采购,3分钟左右您将得到回复。