- 您现在的位置:买卖IC网 > PDF目录268247 > PPC7448VS1267ND (FREESCALE SEMICONDUCTOR INC) 32-BIT, 1267 MHz, RISC PROCESSOR, CBGA360 PDF资料下载

参数资料

| 型号: | PPC7448VS1267ND |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 1267 MHz, RISC PROCESSOR, CBGA360 |

| 封装: | 25 X 25 MM, 2.20 MM HEIGHT, 1.27 MM PITCH, ROHS COMPLIANT, HCTE, CERAMIC, LGA-360 |

| 文件页数: | 12/14页 |

| 文件大小: | 134K |

| 代理商: | PPC7448VS1267ND |

MPC7448 Hardware Specifications Addendum for the MC7448xxnnnnNx Series, Rev. 6

Freescale Semiconductor

7

General Parameters

5.2.1 Clock AC Specifications

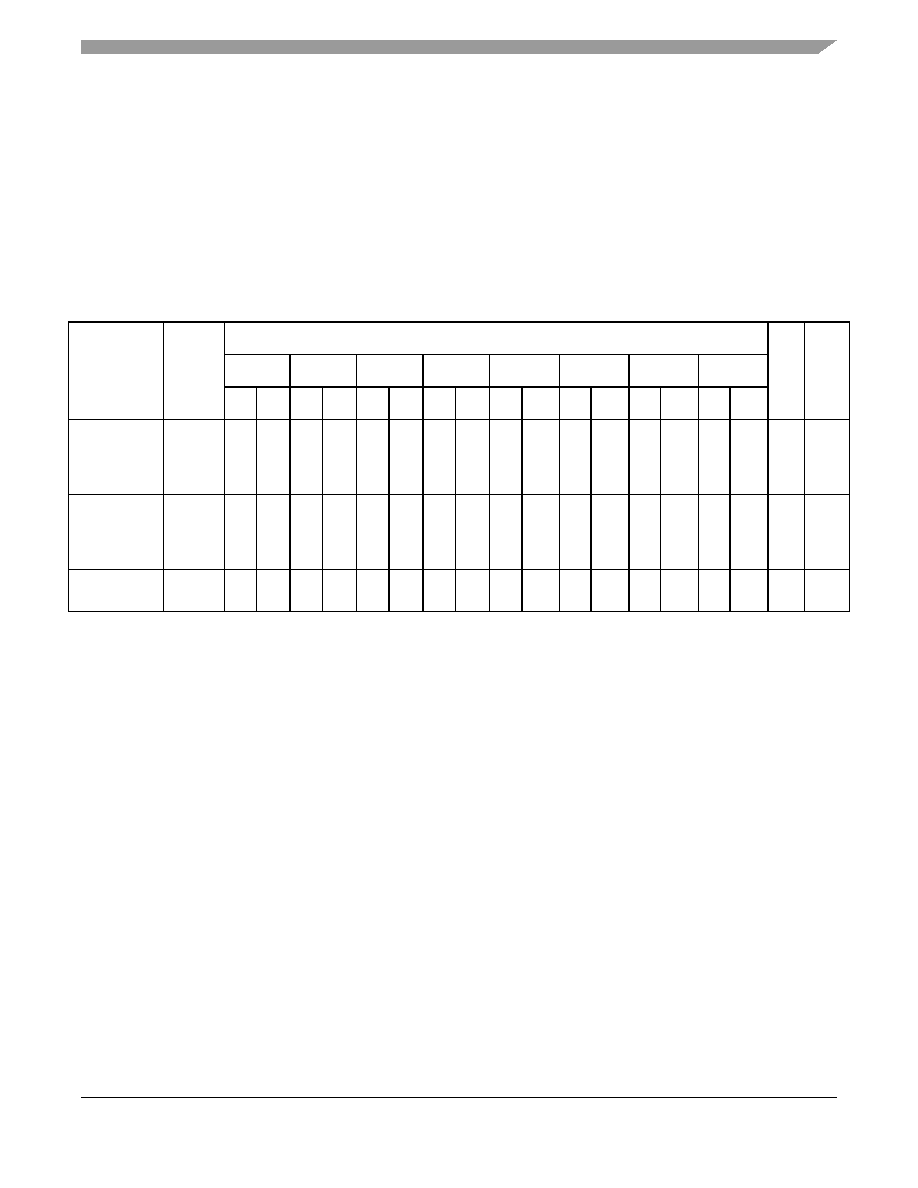

Table 8 provides the clock AC timing specifications for the MPC7448 part numbers discussed here.

NOTE

The core frequency information in this table applies when the device

operates at the nominal core voltage indicated in Table 4. For core

frequency specifications at derated core voltage conditions, see Section 5.3,

Table 8. Clock AC Timing Specifications

At recommended operating conditions. See Table 4.

Characteristic

Symbol

Maximum Processor Core Frequency (MHz)

Unit Notes

600

667

800

867

1000

1250

1267

1400

Min Max Min Max Min Max Min Max Min

Max Min

Max Min Max Min Max

Processor

frequency

DFS mode

disabled

fcore

500 600

500

667

500

800

500

867

500 1000 500 1250 500 1267 500 1400 MHz

1, 8, 9

Processor

frequency

DFS mode

enabled

fcore_DFS 250 300 250 333 250 400 250 433 250 500 250 625 250 633 250 700 MHz

10

VCO

frequency

fVCO

500 600

500

667

500

800

500

867

500 1000 500 1250 500 1267 500 1400 MHz

1, 9

Notes:

1. Caution: The SYSCLK frequency and PLL_CFG[0:5] settings must be chosen such that the resulting SYSCLK (bus) frequency,

processor core frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies.

Refer to the PLL_CFG[0:5] signal description in Section 9.1.1, “PLL Configuration,” in the hardware specifications for valid

PLL_CFG[0:5] settings.

8. This reflects the maximum and minimum core frequencies when the dynamic frequency switching feature (DFS) is disabled.

fcore_DFS provides the maximum and minimum core frequencies in a DFS mode.

9. Caution: These values specify the maximum processor core and VCO frequencies when the device is operated at the nominal

core voltage. If operating the device at the derated core voltage, the processor core and VCO frequencies must be reduced. See

Section 5.3, “Voltage and Frequency Derating,” for more information.

10.This specification supports the Dynamic Frequency Switching (DFS) feature and is applicable only when one of the DFS modes

(divide-by-2 or divide-by-4) is enabled. When DFS is disabled, the core frequency must conform to the maximum and minimum

frequencies stated for fcore.

相关PDF资料 |

PDF描述 |

|---|---|

| PPC7448VS1400NC | 32-BIT, 1400 MHz, RISC PROCESSOR, CBGA360 |

| PIC16LF1936T-E/SP | 8-BIT, FLASH, 32 MHz, RISC MICROCONTROLLER, PDIP28 |

| PIC18LF24J10-E/SO | 8-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PDSO28 |

| PIC16CR73-E/SP | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDIP28 |

| PSD813F4-15JI | 128K X 8 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PPC7450RX600LD | 制造商:Freescale Semiconductor 功能描述: |

| PPC7457RX1000NB | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:PPC7457RX1000NB |

| PPC7457RX600NB | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:PPC7457RX1000NB |

| PPC7457RX733NB | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:PPC7457RX1000NB |

| PPC7457RX867NB | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:PPC7457RX1000NB |

发布紧急采购,3分钟左右您将得到回复。